#### Design of Access Control Mechanisms in SoCs with Formal Integrity Guarantees

USENIX Security Symposium '23 2023-08-10

**Dino Mehmedagić,** Mohammad Rahmani Fadiheh, Johannes Müller, Anna Lena Duque Antón, Dominik Stoffel, Wolfgang Kunz R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

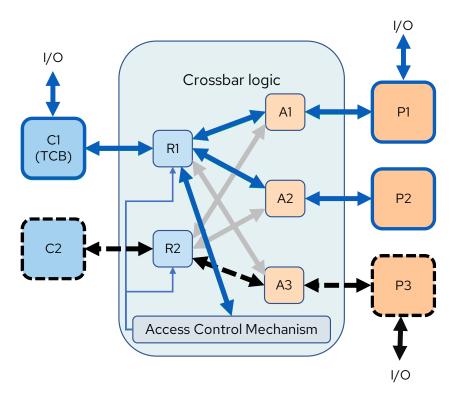

## **Threat Model**

- > Increasing need for SoCs with diversified hardware

- > Third-party IPs  $\rightarrow$  trust issues  $\otimes$

>SoC Access Control Mechanism

- > Domains: <u>High-security</u> vs low-security

- > Access control ensures that communication between domains doesn't endanger security

# **Security Target**

### > Operation integrity:

> Forbidden information flow: <u>low</u> security domain → <u>high security</u> <u>domain outputs</u>

#### >UPEC:

- > Exhaustive verification of information flow restrictions at the RTL

- > Interval Property Checking (IPC)

- > 2-instance (miter) model

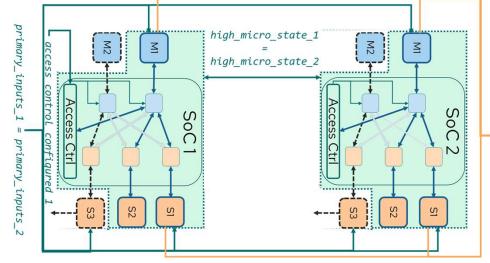

## **UPEC for Operation Integrity**

4

RPTU

ecure

outputs

secure\_outputs\_2

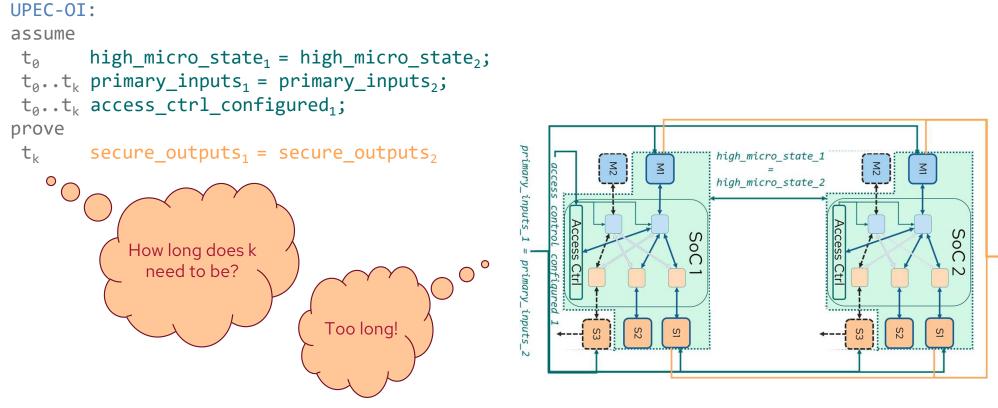

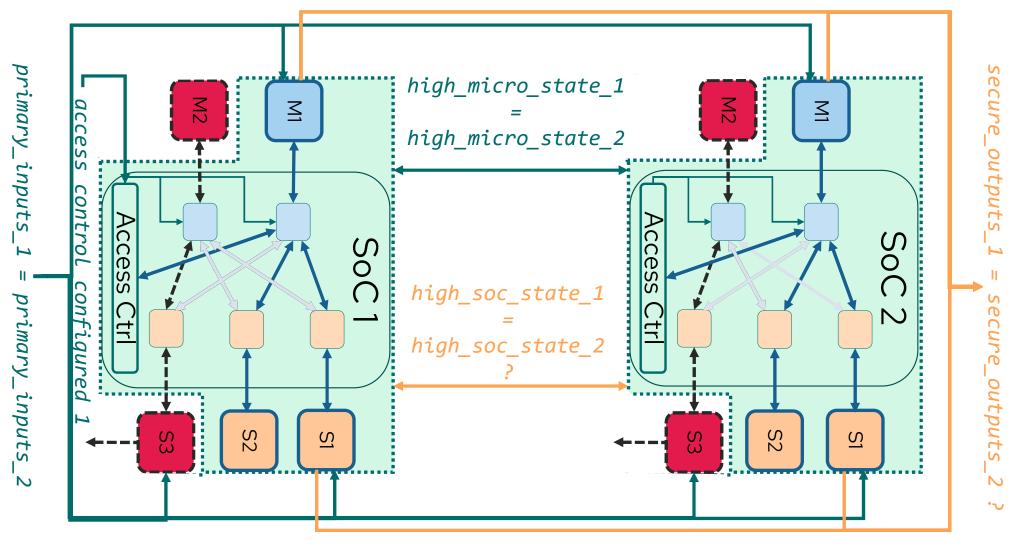

# **Decomposing the Proof**

#### UPEC-OI:

#### assume

```

t<sub>0</sub> high_micro_state<sub>1</sub> = high_micro_state<sub>2</sub>;

t<sub>0</sub>..t<sub>k</sub> primary_inputs<sub>1</sub> = primary_inputs<sub>2</sub>;

t<sub>0</sub>..t<sub>k</sub> access_ctrl_configured<sub>1</sub>;

```

prove

```

t<sub>k</sub> secure_outputs<sub>1</sub> = secure_outputs<sub>2</sub>

t<sub>k</sub> high_soc_state<sub>1</sub> = high_soc_state<sub>2</sub>;

```

RPTU

RPTU

RPTU

RPTU

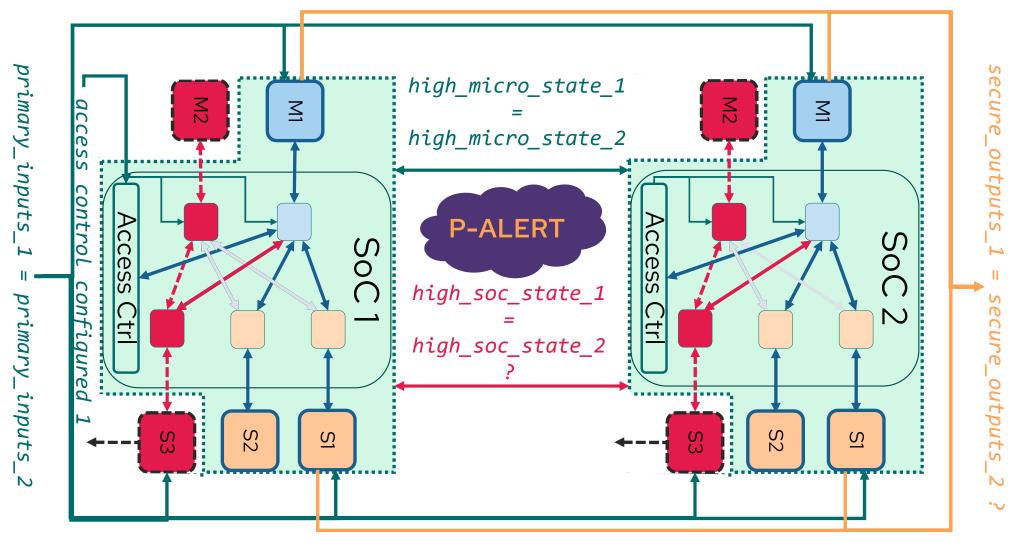

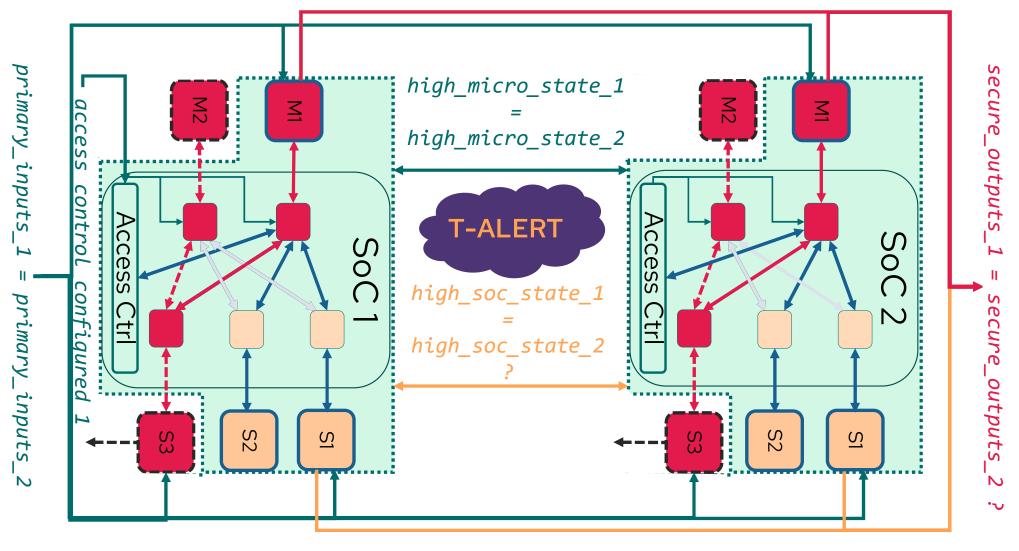

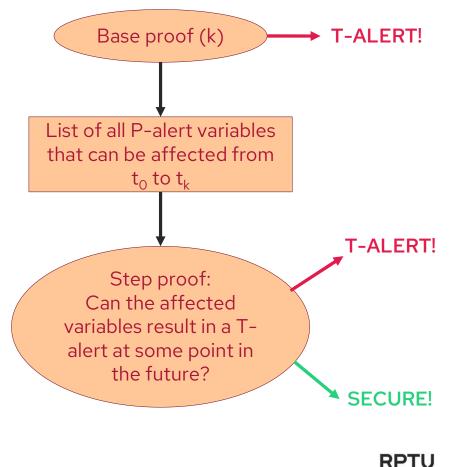

# **UPEC-OI** Verification Methodology

#### >Induction-based approach to completely verify operation integrity

- > Base proof: Find all P-alerts and verify OI for a bounded time window k

- Step proof: Use IPC's symbolic initial state to fast forward to any future time point in which a T-alert can occur

#### >Additional optimizations

- > Sound blackboxing

- > Spatial, temporal decomposition, T-alert trigger expansion...

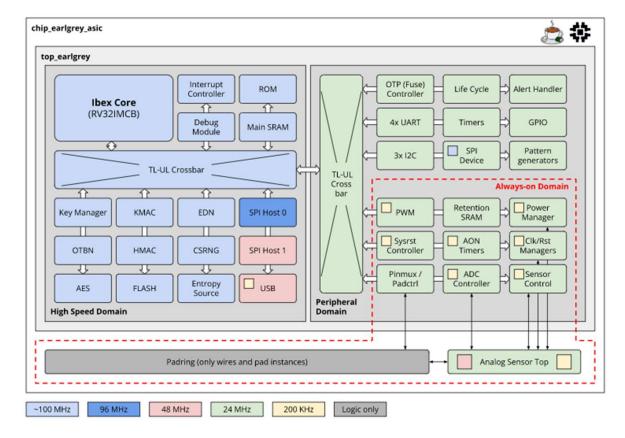

## Case Study: OpenTitan

**UPEC-Driven Design of Access Control**

- > Add malicious IPs to model the threat

- > Equip SoC with access control mechanism in the interconnect

- Refine the access control mechanism through a UPEC-OI-driven design flow

#### **Case Study: Results**

UPEC-Driven Design of Access Control

| Overall design process            | 3 person-months       |

|-----------------------------------|-----------------------|

| Number of verify-patch iterations | 19                    |

| Average property check time       | ~5 minutes            |

| Longest UPEC-OI check time        | 11 hours              |

| Peak memory consumption           | 25 GB                 |

| Design size                       | 14 million state bits |

## Conclusion

- > Developed a methodology to formally verify operation integrity:

- > Property formulation

- > Proof decomposition

- > Scalability and usability optimizations

### > Case study shows: UPEC-OI is feasible for realistic SoCs

More details in the paper "Design of Access Control Mechanisms in Systems-on-Chip with Formal Integrity Guarantees" – available as a preprint on https://www.usenix.org/conference/usenixsecurity23/presentation/mehmedagic

RPTU

# Thank you!

Questions?

Contact me at: dino.mehmedagic@edu.rptu.de