# An Off-Chip Attack on Hardware Enclaves via the Memory Bus

Dayeol Lee<sup>1</sup>, Dongha Jung<sup>3</sup>, Ian T. Fang<sup>1</sup>, Chia-Che Tsai<sup>1,2</sup>, Raluca Ada Popa<sup>1</sup>

- <sup>1</sup> UC Berkeley

- <sup>2</sup> Texas A&M University

- <sup>3</sup> SK Hynix Inc.

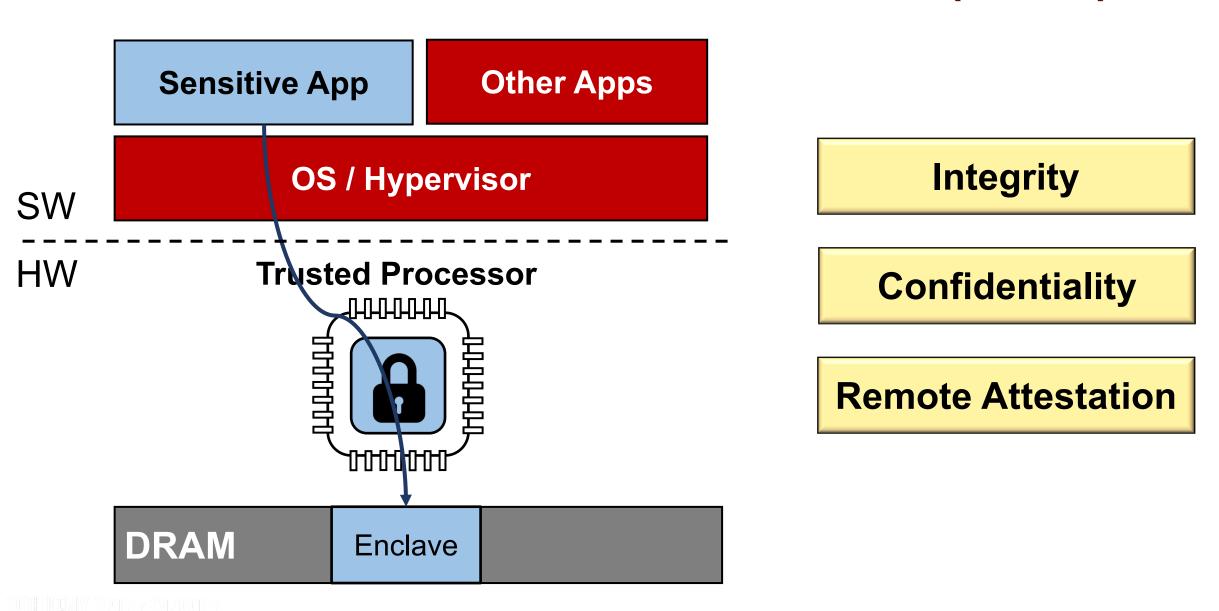

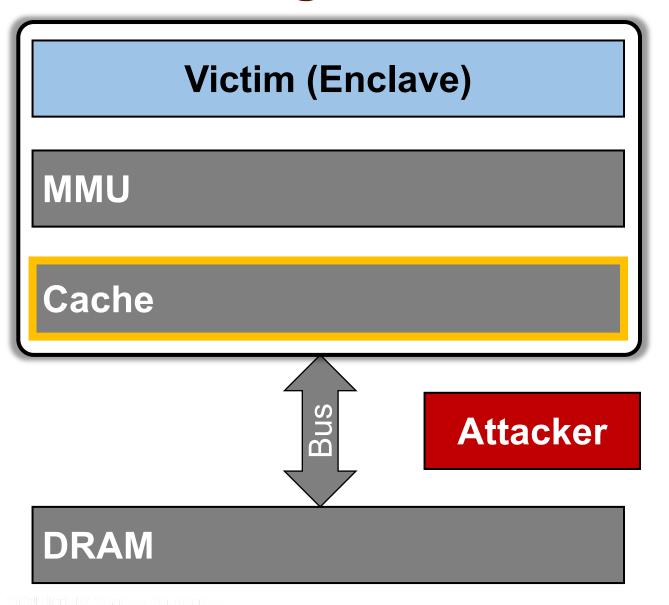

# **Trusted Execution Environments (TEEs)**

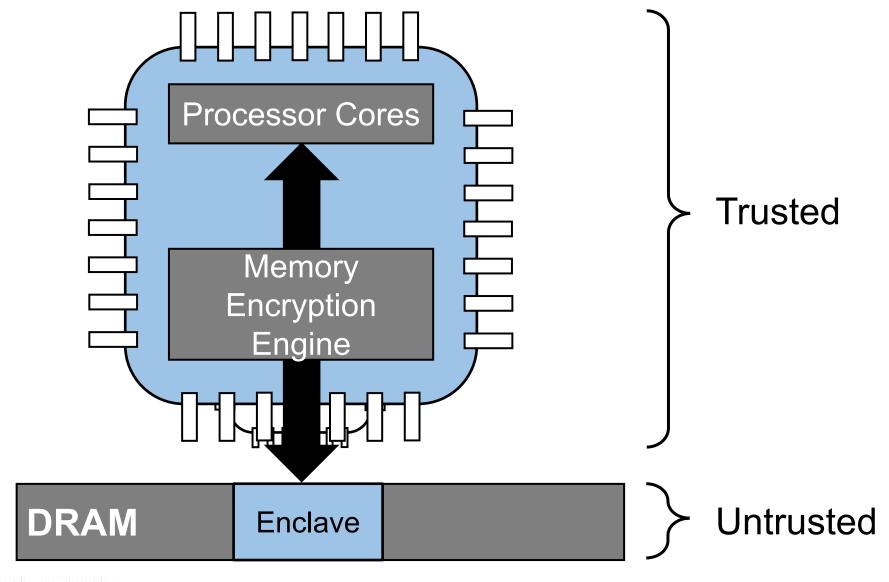

### **Memory Encryption of Intel SGX**

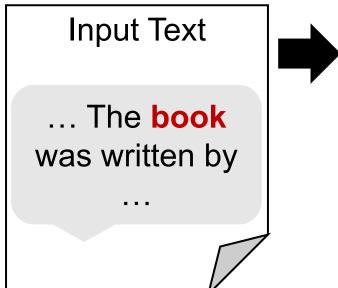

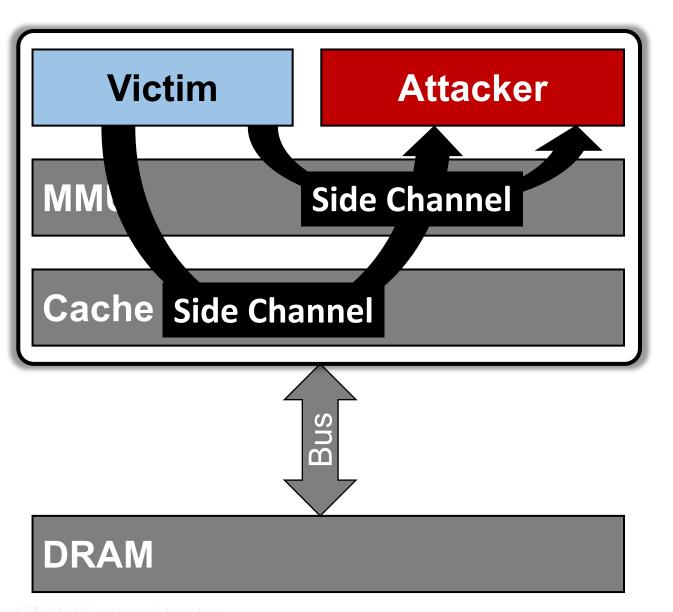

# Access Pattern Leakage via Side Channel

Spell Checker: Hunspell [Xu et al., 17] for each word in input text: **Input Text** dictionary.search(word) Dictionary (Hash Table): table[0] cask book table[1] rich cry

# Access Pattern Leakage via Side Channel

Hunspell [Xu et al., 17]

**Access Pattern:**

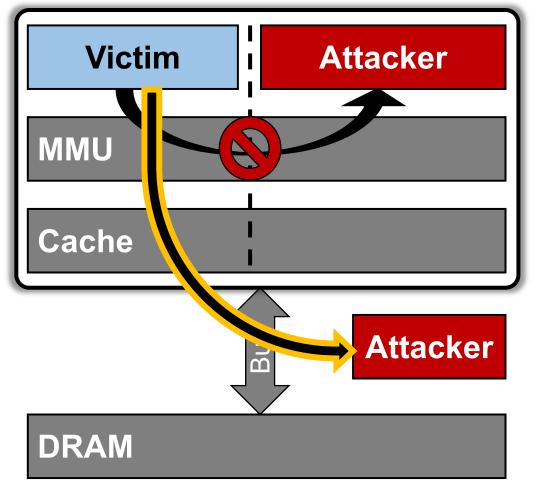

#### Side-Channel Attacks on SGX Enclaves

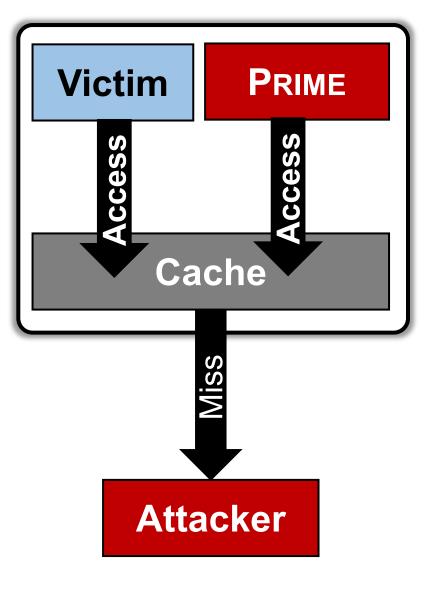

- Cache Side-Channel Attacks

- Brasser'17, Schwarz'17, Moghimi'17, VanBulck'18

- Page Table-Based Attacks

- Controlled-Channel'15, VanBulck'17

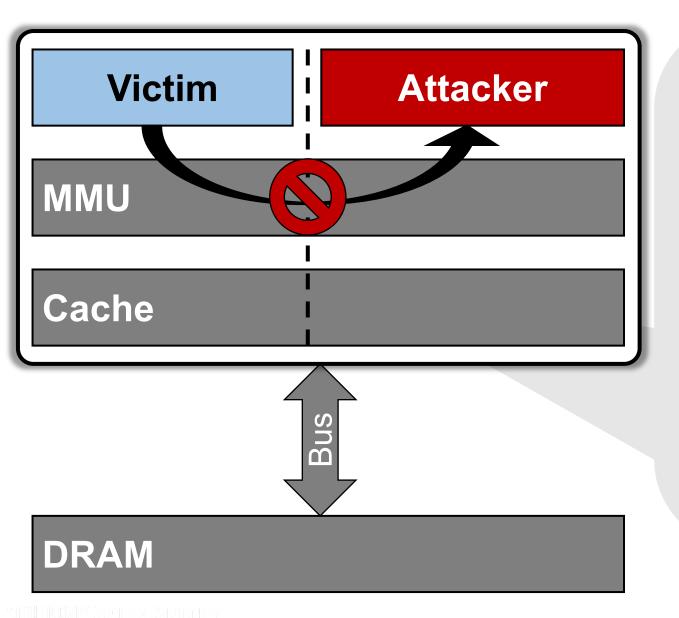

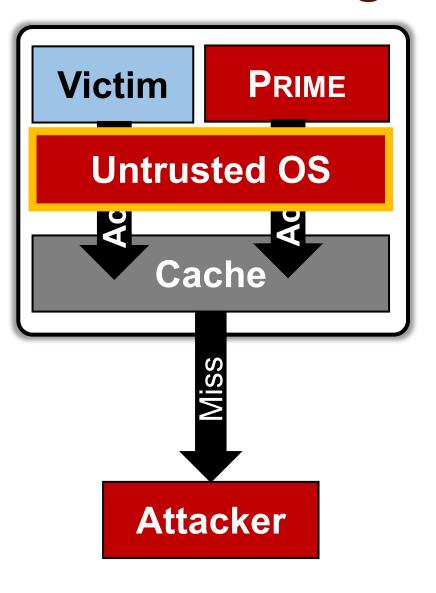

#### Side-Channel Attacks on SGX Enclaves

- Cache Side-Channel Attacks

- Brasser'17, Schwarz'17, Moghimi'17,

VanBulck'18

- Page Table-Based Attacks

- Controlled-Channel'15, VanBulck'17

- Mitigations

- Varys '18, Chen et al.'18, Gruss et al.

'17, T-SGX'17, DéJà Vu '17

- TEEs from Academia

- Keystone'20, Sanctum'16

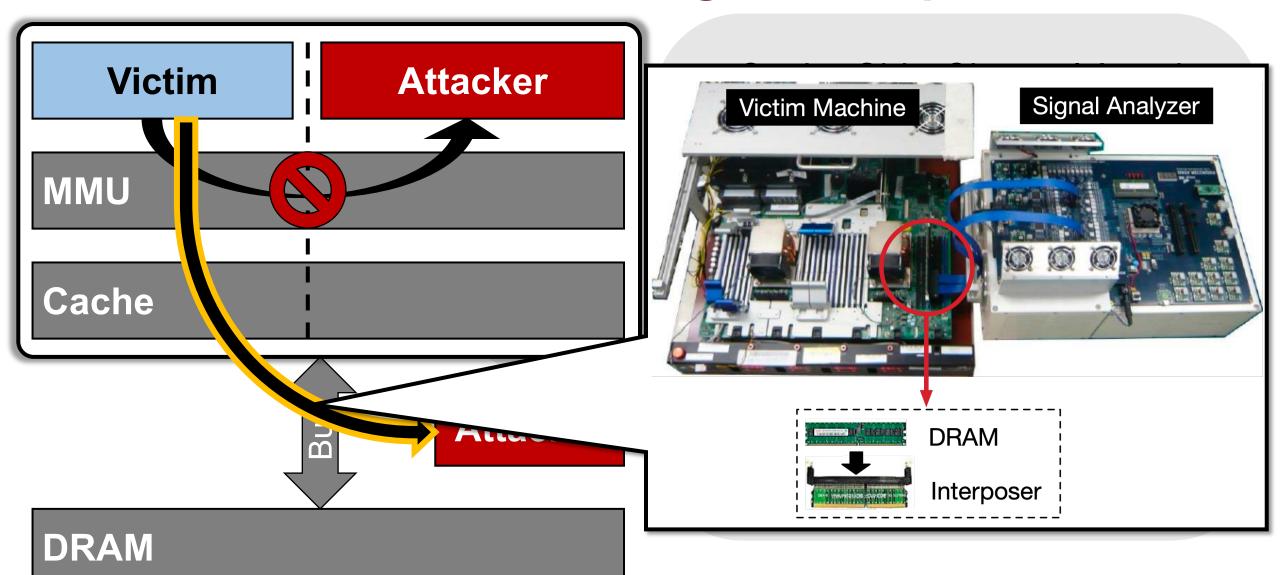

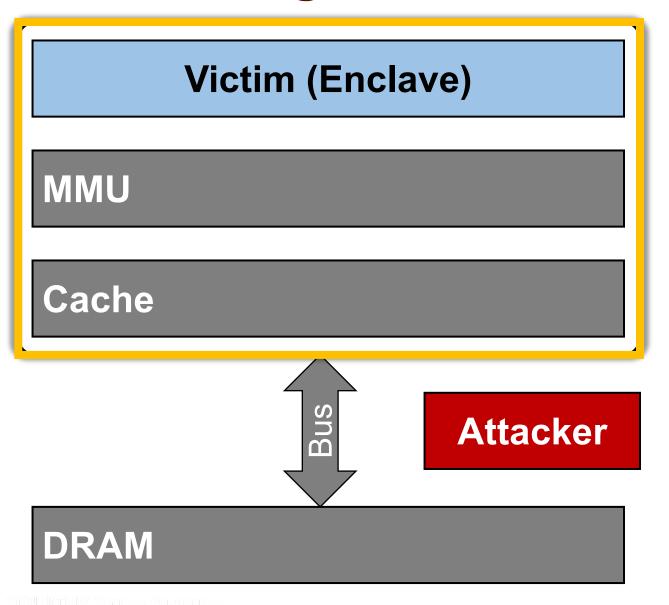

#### MEMBUSTER: Demonstrating "Off-Chip Attack"

#### MEMBUSTER: Demonstrating "Off-Chip Attack"

- Cache Side-Channel Attacks

- Brasser'17, Schwarz'17, Moghimi'17,

VanBulck'18

- Page Table-Based Attacks

- Controlled-Channel'15, VanBulck'17

- Mitigations

- Varys '18, Chen et al.'18, Gruss et al.'17, T-SGX'17, DéJà Vu '17

- TEEs from Academia

- Keystone'20, Sanctum'16

None of these can mitigate

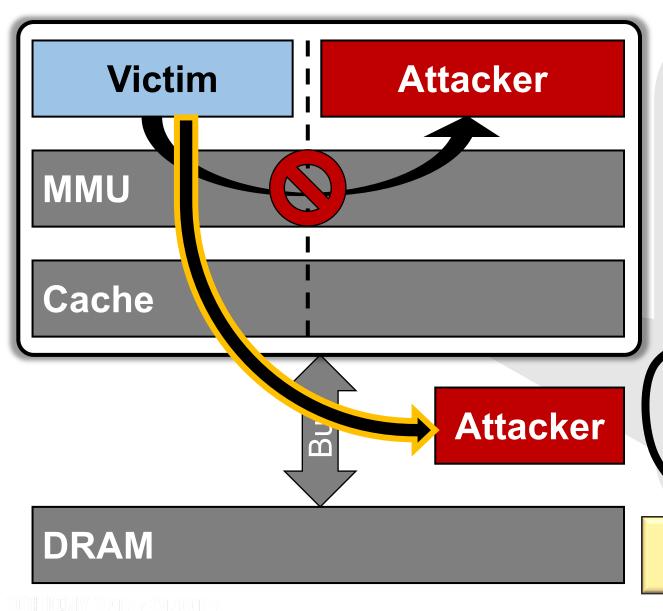

#### MEMBUSTER: Demonstrating "Off-Chip Attack"

- Hard to detect or mitigate on chip

- No interference with SW

- Resource partitioning does not work

- Oblivious memory access

- Performance impact

- Address bus encryption

- Infeasible in commodity DRAM

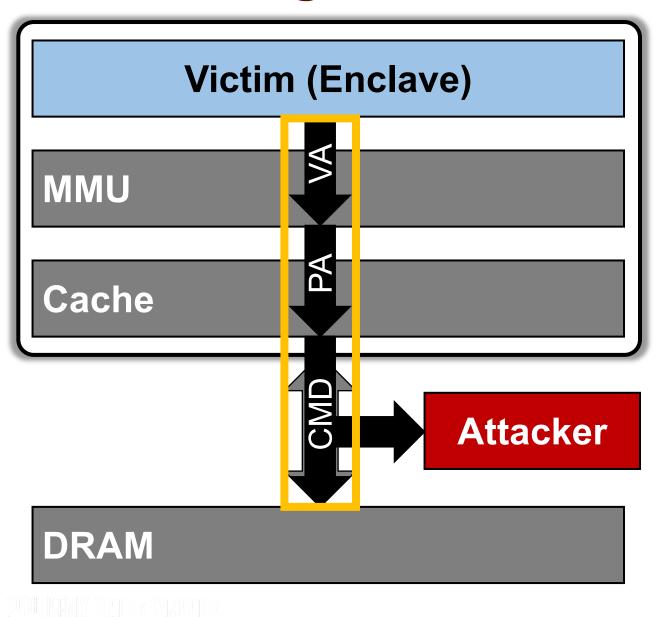

Address Translation and Synchronization

- Address Translation and Synchronization

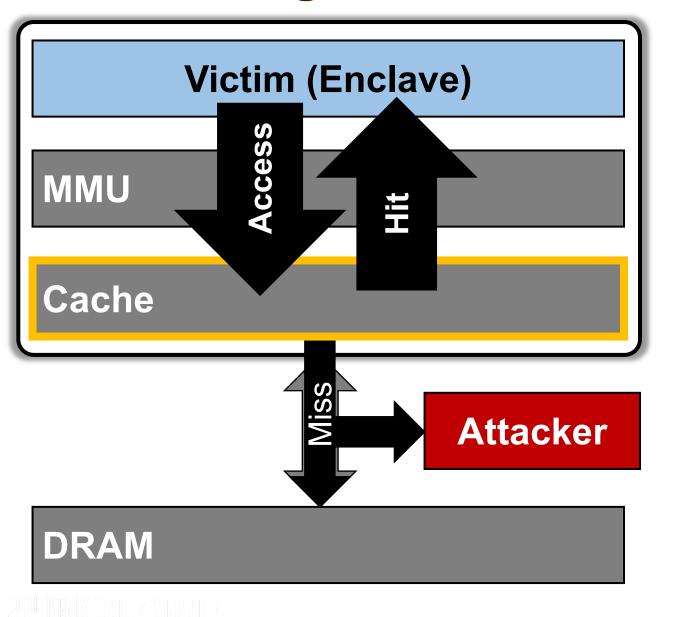

- Lossy Channel due to Cache Hierarchy

- Address Translation and Synchronization

- Lossy Channel due to Cache Hierarchy

- Unusual Behavior in SGX

- Address Translation and Synchronization

- Lossy Channel due to Cache Hierarchy

- Unusual Behavior in SGX

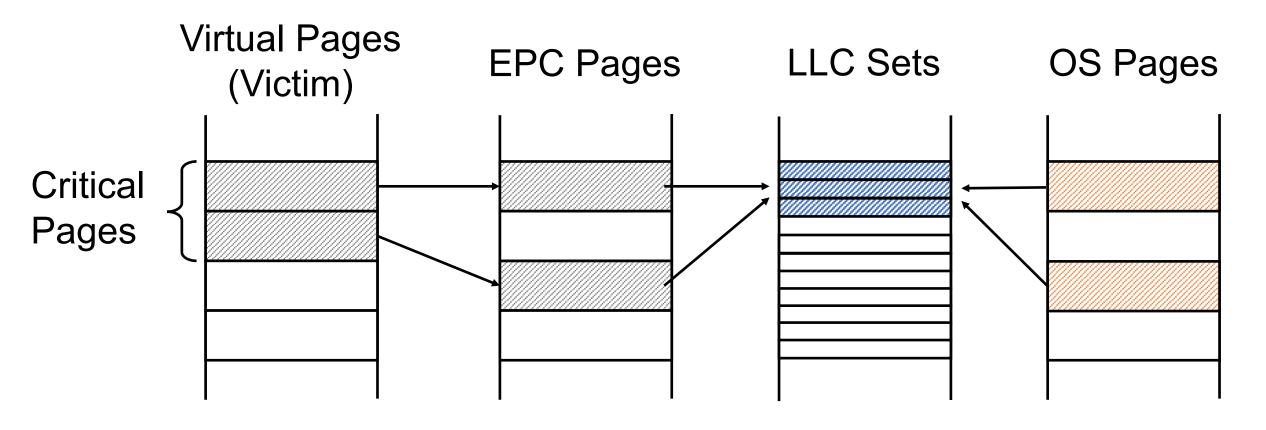

### **Maximizing Side-Channel Information**

- Goal:

- Increase cache misses

- Avoid detectable interference

- Cross-core cache priming

- Cache eviction in PRIME+PROBE Attack

- Problems

- Insufficient memory access bandwidth

- Large last-level cache

- Hundreds of milliseconds to evict all

#### **Maximizing Side-Channel Information**

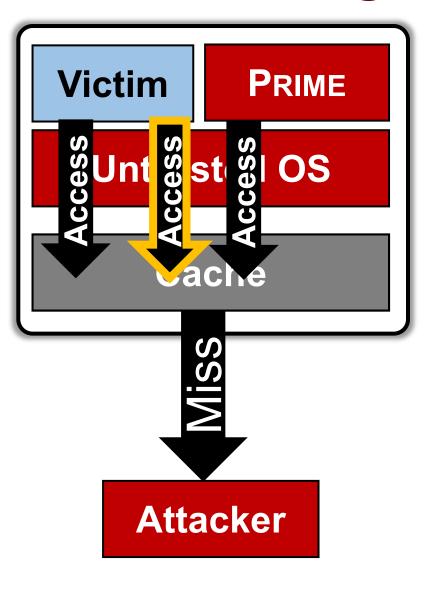

Observation 1

The address mapping is untrusted

### **Maximizing Side-Channel Information**

- Observation 1

- The address mapping is untrusted

- Observation 2

The attacker only needs to observe "critical" memory accesses

Idea: Squeeze the Cache!

# Cache Squeezing in a Nutshell

No interrupt nor fault

Small slowdown

#### **Evaluation**

#### Hardware

- Intel i5-8400 (Coffee Lake)

- LLC: 9MB, 6-slice, 12-way set associative, 2048 sets

- DRAM: Non-ECC DDR4-2400 UDIMM 8GB

- Interposer/signal analyzer from SK Hynix

#### Software

- Two attack examples: Hunspell and Memcached

- Graphene-SGX with unmodified victim application

- Modified SGX driver for cache squeezing

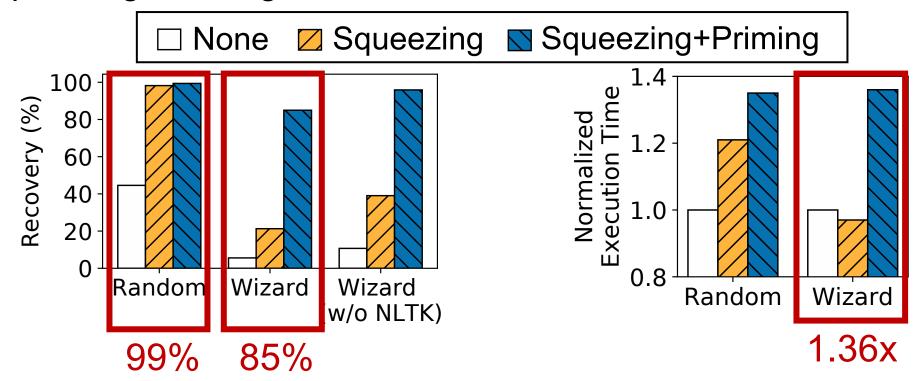

#### **Hunspell Attack Results**

- Randomly-generated words (Random) and Wizard of Oz (Wizard)

- Squeezing+Priming recovers most of the data

No interference: hard to detect with on-chip techniques

#### Conclusion

- Membuster: an off-chip attack via the memory bus

- Performed on commodity CPU and DRAM

- Non-interfering with victim application

- Previous on-chip solutions or other TEEs do not defeat the attack

- Costly mitigation techniques

- Oblivious memory access

- Alternative TEE architecture (e.g., memory bus encryption)

**Thank You!**

# **Thank You!**

Dayeol Lee (<u>dayeol@berkeley.edu</u>)

Chia-Che Tsai (<u>chiache@tamu.edu</u>)

Raluca Ada Popa (<u>raluca.popa@berkeley.edu</u>)