#### **USENIX** Association

# Proceedings of the 2020 USENIX Annual Technical Conference

# © 2020 by The USENIX Association All Rights Reserved This volume is published as a collective work. Rights to individual papers remain with the author or the author's employer. Permission is granted for the noncommercial reproduction of the complete work for educational or research purposes. Permission is granted to print, primarily for one person's exclusive use, a single copy of these Proceedings. USENIX acknowledges all trademarks herein. ISBN 978-1-939133-14-4

Cover Image created by freevector.com and distributed under the Creative Commons Attribution-ShareAlike 4.0

license (https://creativecommons.org/licenses/by-sa/4.0/).

#### **Conference Organizers**

**Program Co-Chairs**

Ada Gavrilovska, Georgia Institute of Technology

Erez Zadok, Stony Brook University

**Program Committee Leaders**

Aruna Balasubramanian, Stony Brook University

Donald Porter, The University of North Carolina at Chapel Hill

Liuba Shrira, *Brandeis University* Swaminathan Sundararaman, *Pyxeda AI* Vasily Tarasov, *IBM Research-Almaden*

**Program Committee**

Sangeetha Abdu Jyothi, VMware Research and University of

California, Irvine

Rachit Agarwal, Cornell University

Nitin Agrawal, *ThoughtSpot* Irfan Ahmad, *CachePhysics* Gustavo Alonso, *ETH Zurich* Deniz Altinbuken, *Google*

George Amvrosiadis, Carnegie Mellon University

Andrea Arpaci-Dusseau, University of Wisconsin-Madison

Behnaz Arzani, Microsoft Research

Mona Attariyan, Google

Anirudh Badam, Microsoft Research Saurabh Bagchi, Purdue University

Antonio Barbalace, Stevens Institute of Technology

Ran Ben Basat, Harvard University

Orna Agmon Ben-Yehuda, Technion—Israel Institute of

Technology

Pramod Bhatotia, University of Edinburgh

Ken Birman, Cornell University Sergey Blagodurov, AMD Research Herbert Bos, Vrije Universiteit Amsterdam

James Bottomley, *IBM Research* Kevin Butler, *University of Florida* Yinzhi Cao, *Johns Hopkins University*

Zhen Cao, Google

Feng Chen, Louisiana State University

Ming Chen, Google

Young-ri Choi, Ulsan National Institute of Science and Technology (UNIST)

Guilherme Cox, Nvidia

Heming Cui, The University of Hong Kong (HKU)

Dilma Da Silva, Texas A&M University

Alex Daglis, Georgia Institute of Technology

David Devescery, Georgia Institute of Technology

Abhinav Duggal, Dell EMC

Michael Ferdman, Stony Brook University

Pedro Fonseca, *Purdue University* Moshe Gabel, *University of Toronto*

Manya Ghobadi, Massachusetts Institute of Technology

Jana Giceva, Imperial College London Ashvin Goel, University of Toronto

Xiaohui (Helen) Gu, North Carolina State University

Vishakha Gupta-Cledat, ApertureData

Andreas Haeberlen, University of Pennsylvania

Dongsu Han, Korea Advanced Institute of Science and

Technology (KAIST)

Danny Harnik, IBM Research-Haifa

Tim Harris, Amazon

Eshcar Hillel, Yahoo Research

Michio Honda, University of Edinburgh

Yu Hua, Huazhong University of Science and Technology Jian Huang, The University of Illinois at Urbana-Champaign

Trent Jaeger, The Pennsylvania State University

Bill Jannen, Williams College

Junchen Jiang, University of Chicago Changhee Jung, Purdue University Sudarsun Kannan, Rutgers University Baris Kasikci, University of Michigan

Idit Keidar, Technion-Israel Institute of Technology

Ana Klimovic, *Google Brain*Michael Kozuch, *Intel Labs*Orran Krieger, *Boston University*Mohan Kumar Kumar, *Facebook*

Youngjin Kwon, Korea Advanced Institute of Science and

Technology (KAIST) Julia Lawall, Inria/LIP6

Philip Levis, Stanford University Felix Lin, Purdue University

Heiner Litz, University of California, Santa Cruz

Vincent Liu, *University of Pennsylvania* Brandon Lucia, *Carnegie Mellon University*

Xiaosong Ma, Qatar Computing Research Institute (QCRI), HBKU, Qatar

Peter Macko, NetApp

Harsha V. Madhyastha, *University of Michigan* Carlos Maltzahn, *University of California, Santa Cruz*

Alexander Merritt, *Intel*Michael Mesnier, *Intel Labs*

Changwoo Min, Virginia Polytechnic Institute and State University

Shuai Mu, Stony Brook University

Gilles Muller, Inria

Kiran-Kumar Muniswamy-Reddy, *Oracle* Srinivasan Narayanamurthy, *NetApp*

Ravi Netravali, University of California, Los Angeles

Radhika Niranjan Mysore, VMware Research

Roberto Palmieri, Lehigh University Aurojit Panda, New York University

Gabriel Parmer, George Washington University

Raju Rangaswami, Florida International University

Oriana Riva, Microsoft Research

Amitabha Roy, *Google* Larry Rudolph, *Two Sigma*

Jack Sampson, *The Pennsylvania State University* Mahadev Satyanarayanan, *Carnegie Mellon University*

Jiri Schindler, Tranquil Data

Malte Schwarzkopf, Brown University

Russell Sears, Apple

Siddhartha Sen, Microsoft Research

Philip Shilane, Dell EMC

Mark Silberstein, Technion—Israel Institute of Technology

Richard Spillane, VMware Research Scott Stoller, Stony Brook University

Patrick Stuedi, LinkedIn

Lalith Suresh, VMware Research Amy Tai, VMware Research Eno Thereska, Amazon

Theodore Ts'o, Google

Alexey Tumanov, Georgia Institute of Technology

Keval Vora, Simon Fraser University

Ric Wheeler, Facebook

Avani Wildani, Emory University

Emmett Witchel, The University of Texas at Austin

Yue Yang, Micron Technology Ming Zhao, Arizona State University

Lin Zhong, Rice University

Noa Zilberman, University of Oxford

#### **External Review Committee**

Raja Appuswamy, EURECOM, Sophia Antipolis

Muli Ben-Yehuda, LightBits Labs

Angela Demke Brown, University of Toronto

Sindhu Ghanta, Pyxeda Inc.

Gernot Heiser, UNSW Sydney

Paul E. McKenney, IBM Linux Technology Center

Ethan Miller, University of California, Santa Cruz, and Pure Storage

Dalit Naor, IBM Research—Haifa

Youjip Won, Korea Advanced Institute of Science and

Technology (KAIST)

Gala Yadgar, Technion-Israel Institute of Technology

#### **Submissions Co-Chairs**

Ketan Bhardwaj, Georgia Institute of Technology

Dongyoon Lee, Stony Brook University

#### **External Reviewers**

Amogh Akshintala Ali Anwar Avi Asayag Gal Assa Jia-Ju Bai Lauren Bindschaedler Yuval Cassuto Joanna Che Yitao Chen Peter Chubb Shir Cohen

Dave Dice Babak Esmaeili Sungho Hong Trammell Hudson Kasra Jamshidi Runvu Jin Geoff Kuenning Eugene Kuznetsov Yubo Liu Mugilan Mariappan Matthew Morrison

Oded Naor Arik Rinberg Donour Sizemore Weijia Song Lynus Vaz Tianzheng Wang David Yakira Qirui Yang Yiting Yao Ding Yuan Kaiqi Zhao

#### **2020 USENIX Annual Technical Conference**

#### July 15–17, 2020

| USENIX ATC '20 Program Co-Chairs Message x                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wednesday, July 15                                                                                                                                                                                                                                                                                                                                      |

| The Non-Volatile One                                                                                                                                                                                                                                                                                                                                    |

| <b>Libnvmmio: Reconstructing Software IO Path with Failure-Atomic Memory-Mapped Interface</b>                                                                                                                                                                                                                                                           |

| MatrixKV: Reducing Write Stalls and Write Amplification in LSM-tree Based KV Stores with Matrix Container                                                                                                                                                                                                                                               |

| in NVM  Ting Yao, Yiwen Zhang, and Jiguang Wan, Huazhong University of Science and Technology; Qiu Cui and Liu Tang, PingCAP; Hong Jiang, UT Arlington; Changsheng Xie, Huazhong University of Science and Technology; Xubin He, Temple University                                                                                                      |

| Disaggregating Persistent Memory and Controlling Them Remotely: An Exploration of Passive Disaggregated                                                                                                                                                                                                                                                 |

| Key-Value Stores                                                                                                                                                                                                                                                                                                                                        |

| SplinterDB: Closing the Bandwidth Gap for NVMe Key-Value Stores                                                                                                                                                                                                                                                                                         |

| Twizzler: a <i>Data-Centric</i> OS for Non-Volatile Memory                                                                                                                                                                                                                                                                                              |

| The Data Center One                                                                                                                                                                                                                                                                                                                                     |

| BASTION: A Security Enforcement Network Stack for Container Networks                                                                                                                                                                                                                                                                                    |

| Spool: Reliable Virtualized NVMe Storage Pool in Public Cloud Infrastructure                                                                                                                                                                                                                                                                            |

| HDDse: Enabling High-Dimensional Disk State Embedding for Generic Failure Detection System of Heterogeneous                                                                                                                                                                                                                                             |

| Disks in Large Data Centers                                                                                                                                                                                                                                                                                                                             |

| Adaptive Placement for In-memory Storage Functions                                                                                                                                                                                                                                                                                                      |

| NetKernel: Making Network Stack Part of the Virtualized Infrastructure. 143 Zhixiong Niu, Microsoft Research; Hong Xu, City University of Hong Kong; Peng Cheng, Microsoft Research; Qiang Su, City University of Hong Kong; Yongqiang Xiong, Microsoft Research; Tao Wang, New York University; Dongsu Han, KAIST; Keith Winstein, Stanford University |

| The Cloudy One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Platinum: A CPU-Efficient Concurrent Garbage Collector for Tail-Reduction of Interactive Services 159 Mingyu Wu, Ziming Zhao, Yanfei Yang, Haoyu Li, Haibo Chen, Binyu Zang, and Haibing Guan, Shanghai Jiao Tong University; Sanhong Li, Chuansheng Lu, and Tongbao Zhang, Alibaba                                                                                                                                                                                                                                                                 |

| PinK: High-speed In-storage Key-value Store with Bounded Tails                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Optimus Cloud: Heterogeneous Configuration Optimization for Distributed Databases in the Cloud                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Serverless in the Wild: Characterizing and Optimizing the Serverless Workload at a Large Cloud Provider 205 Mohammad Shahrad, Rodrigo Fonseca, Íñigo Goiri, Gohar Chaudhry, Paul Batum, Jason Cooke, Eduardo Laureano, Colby Tresness, Mark Russinovich, and Ricardo Bianchini, <i>Microsoft Azure and Microsoft Research</i>                                                                                                                                                                                                                       |

| Lessons Learned from the Chameleon Testbed. 219 Kate Keahey, Argonne National Laboratory; Jason Anderson and Zhuo Zhen, University of Chicago; Pierre Riteau, StackHPC Ltd; Paul Ruth, RENCI UNC Chapel Hill; Dan Stanzione, Texas Advanced Computing Center; Mert Cevik, RENCI UNC Chapel Hill; Jacob Colleran and Haryadi S. Gunawi, University of Chicago; Cody Hammock, Texas Advanced Computing Center; Joe Mambretti, Northwestern University; Alexander Barnes, François Halbah, Alex Rocha, and Joe Stubbs, Texas Advanced Computing Center |

| The Buggy One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPINFER: Inferring Semantic Patches for the Linux Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

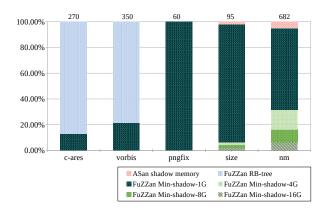

| FuZZan: Efficient Sanitizer Metadata Design for Fuzzing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

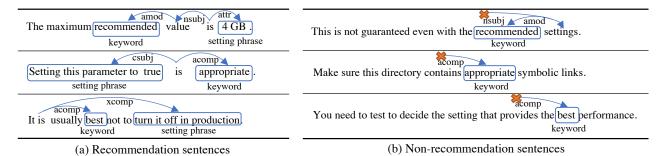

| PracExtractor: Extracting Configuration Good Practices from Manuals to Detect Server Misconfigurations 265 Chengcheng Xiang and Haochen Huang, <i>University of California San Diego</i> ; Andrew Yoo, <i>University of Illinois at Urbana-Champaign</i> ; Yuanyuan Zhou, <i>University of California</i> , <i>San Diego</i> ; Shankar Pasupathy, <i>NetApp</i>                                                                                                                                                                                     |

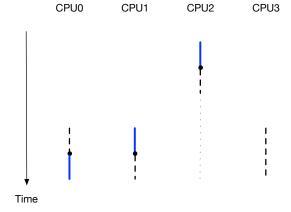

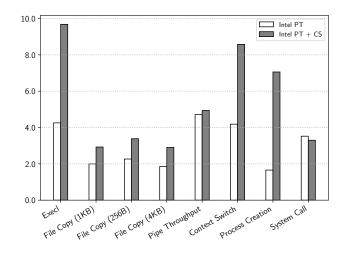

| Reverse Debugging of Kernel Failures in Deployed Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Offload Annotations: Bringing Heterogeneous Computing to Existing Libraries and Workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Thursday, July 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The Machine Learning One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HetPipe: Enabling Large DNN Training on (Whimpy) Heterogeneous GPU Clusters through Integration of Pipelined Model Parallelism and Data Parallelism                                                                                                                                                                                                                                                                                                                                                                                                 |

| AutoSys: The Design and Operation of Learning-Augmented Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Daydream: Accurately Estimating the Efficacy of Performance Optimizations for DNN Training                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ALERT: Accurate Learning for Energy and Timeliness                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NeuOS: A Latency-Predictable Multi-Dimensional Optimization Framework for DNN-driven Autonomous                                                                                                                               |

| Systems                                                                                                                                                                                                                       |

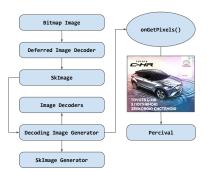

| Percival: Making In-Browser Perceptual Ad Blocking Practical with Deep Learning                                                                                                                                               |

| The OS and Virtualization One                                                                                                                                                                                                 |

| Harmonizing Performance and Isolation in Microkernels with Efficient Intra-kernel Isolation and Communication 401 Jinyu Gu, Xinyue Wu, Wentai Li, Nian Liu, Zeyu Mi, Yubin Xia, and Haibo Chen, Shanghai Jiao Tong University |

| FAASM: Lightweight Isolation for Efficient Stateful Serverless Computing                                                                                                                                                      |

| Fewer Cores, More Hertz: Leveraging High-Frequency Cores in the OS Scheduler for Improved Application                                                                                                                         |

| <b>Performance</b>                                                                                                                                                                                                            |

| vSMT-IO: Improving I/O Performance and Efficiency on SMT Processors in Virtualized Clouds                                                                                                                                     |

| Lightweight Preemptible Functions                                                                                                                                                                                             |

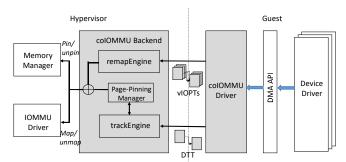

| coIOMMU: A Virtual IOMMU with Cooperative DMA Buffer Tracking for Efficient Memory Management in                                                                                                                              |

| Direct I/O                                                                                                                                                                                                                    |

| The WAN One                                                                                                                                                                                                                   |

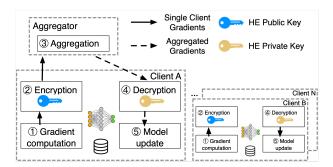

| BatchCrypt: Efficient Homomorphic Encryption for Cross-Silo Federated Learning                                                                                                                                                |

| A Deep Dive into DNS Query Failures                                                                                                                                                                                           |

| A Decentralized Blockchain with High Throughput and Fast Confirmation                                                                                                                                                         |

| <b>Reconstructing proprietary video streaming algorithms</b>                                                                                                                                                                  |

| Midgress-aware traffic provisioning for content delivery                                                                                                                                                                      |

| The One about Big Data                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

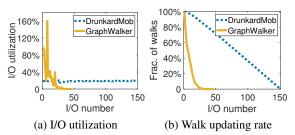

| GraphWalker: An I/O-Efficient and Resource-Friendly Graph Analytic System for Fast and Scalable Random Walks                                                                                                                                                                                                       |

| Rui Wang and Yongkun Li, <i>University of Science and Technology of China</i> ; Hong Xie, <i>Chongqing University</i> ; Yinlong Xu, <i>University of Science and Technology of China</i> ; John C. S. Lui, <i>The Chinese University of Hong Kong</i>                                                              |

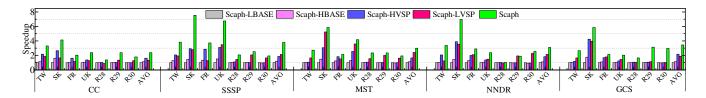

| Scaph: Scalable GPU-Accelerated Graph Processing with Value-Driven Differential Scheduling                                                                                                                                                                                                                         |

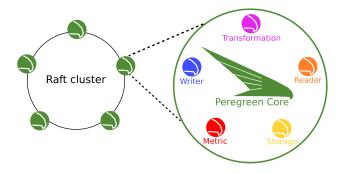

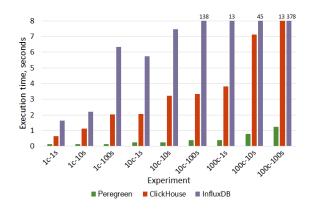

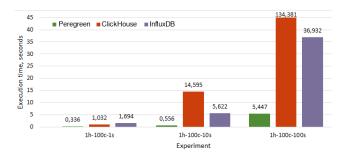

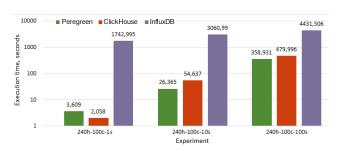

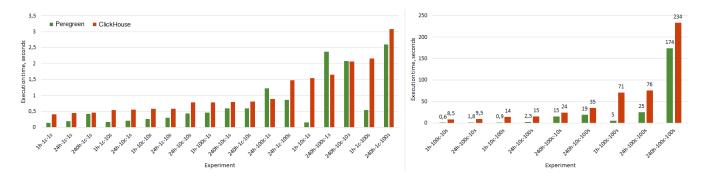

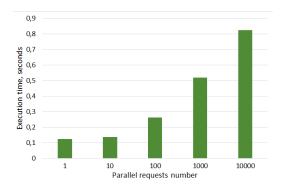

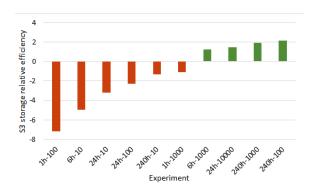

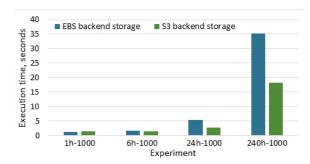

| Peregreen – modular database for efficient storage of historical time series in cloud environments                                                                                                                                                                                                                 |

| AC-Key: Adaptive Caching for LSM-based Key-Value Stores                                                                                                                                                                                                                                                            |

| Posh: A Data-Aware Shell                                                                                                                                                                                                                                                                                           |

| Friday, July 17                                                                                                                                                                                                                                                                                                    |

| The One about Acceleration                                                                                                                                                                                                                                                                                         |

| <b>FineStream: Fine-Grained Window-Based Stream Processing on CPU-GPU Integrated Architectures</b>                                                                                                                                                                                                                 |

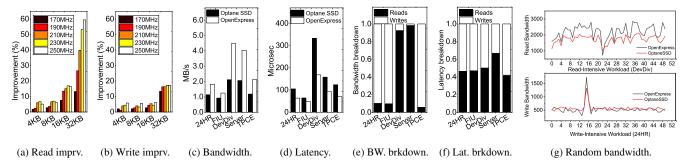

| <b>OpenExpress: Fully Hardware Automated Open Research Framework for Future Fast NVMe Devices 649</b> Myoungsoo Jung, <i>KAIST</i>                                                                                                                                                                                 |

| Fast Software Cache Design for Network Appliances                                                                                                                                                                                                                                                                  |

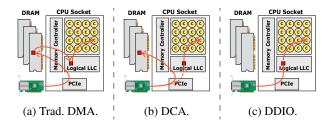

| Reexamining Direct Cache Access to Optimize I/O Intensive Applications for Multi-hundred-gigabit Networks 673 Alireza Farshin, KTH Royal Institute of Technology; Amir Roozbeh, KTH Royal Institute of Technology and Ericsson Research; Gerald Q. Maguire Jr. and Dejan Kostić, KTH Royal Institute of Technology |

| sRDMA – Efficient NIC-based Authentication and Encryption for Remote Direct Memory Access                                                                                                                                                                                                                          |

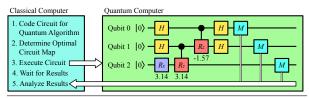

| UREQA: Leveraging Operation-Aware Error Rates for Effective Quantum Circuit Mapping on NISQ-Era Quantum                                                                                                                                                                                                            |

| Computers                                                                                                                                                                                                                                                                                                          |

| The One about Storage                                                                                                                                                                                                                                                                                              |

| Austere Flash Caching with Deduplication and Compression                                                                                                                                                                                                                                                           |

| <b>DADI: Block-Level Image Service for Agile and Elastic Application Deployment</b>                                                                                                                                                                                                                                |

| Efficient Miss Ratio Curve Computation for Heterogeneous Content Popularity                                                                                                                                                                                                                                        |

| Can Applications Recover from fsync Failures?                                                                                                                                                                                                                                                                      |

| <b>DupHunter: Flexible High-Performance Deduplication for Docker Registries</b> Nannan Zhao, Hadeel Albahar, Subil Abraham, and Keren Chen, <i>Virginia Tech;</i> Vasily Tarasov, Dimitrios Skourtis, Lukas Rupprecht, and Ali Anwar, <i>IBM Research—Almaden;</i> Ali R. Butt, <i>Virginia Tech</i>                    |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| OSCA: An Online-Model Based Cache Allocation Scheme in Cloud Block Storage Systems                                                                                                                                                                                                                                      | 785 |

| The Memorable One                                                                                                                                                                                                                                                                                                       |     |

| Lock-free Concurrent Level Hashing for Persistent Memory                                                                                                                                                                                                                                                                | 799 |

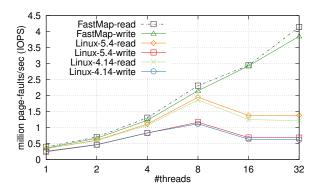

| Optimizing Memory-mapped I/O for Fast Storage Devices                                                                                                                                                                                                                                                                   | 813 |

| A Comprehensive Analysis of Superpage Management Mechanisms and Policies                                                                                                                                                                                                                                                | 829 |

| Effectively Prefetching Remote Memory with Leap                                                                                                                                                                                                                                                                         | 843 |

| <b>go-pmem: Native Support for Programming Persistent Memory in Go.</b> Jerrin Shaji George, Mohit Verma, Rajesh Venkatasubramanian, and Pratap Subrahmanyam, <i>VMware</i>                                                                                                                                             | 859 |

| End the Senseless Killing: Improving Memory Management for Mobile Operating Systems                                                                                                                                                                                                                                     | 873 |

| The One on the Edge                                                                                                                                                                                                                                                                                                     |     |

| Retwork: Exploring Reader Network with COTS RFID Systems                                                                                                                                                                                                                                                                | 889 |

| Acclaim: Adaptive Memory Reclaim to Improve User Experience in Android Systems                                                                                                                                                                                                                                          |     |

| SweynTooth: Unleashing Mayhem over Bluetooth Low Energy                                                                                                                                                                                                                                                                 | 911 |

| Fine-Grained Isolation for Scalable, Dynamic, Multi-tenant Edge Clouds  Yuxin Ren, The George Washington University; Guyue Liu, Carnegie Mellon University; Vlad Nitu, INSA Lyon France; Wenyuan Shao, Riley Kennedy, Gabriel Parmer, and Timothy Wood, The George Washington University; Alain Tchana, ENS Lyon France | 927 |

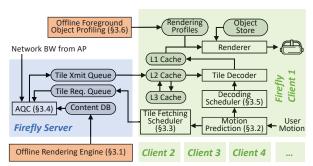

| Firefly: Untethered Multi-user VR for Commodity Mobile Devices.  Xing Liu, University of Minnesota, Twin Cities; Christina Vlachou, Hewlett Packard Labs; Feng Qian and Chendong Wang, University of Minnesota, Twin Cities; Kyu-Han Kim, Hewlett Packard Labs                                                          | 943 |

|                                                                                                                                                                                                                                                                                                                         |     |

## Message from the USENIX ATC '20 Program Co-Chairs

#### 1. Preamble

Every year, conference chairs share their thoughts about the conference. This is often chock-full of statistics about acceptance rates, etc. We'll include stats for sure. We felt, however, that we'd like to share with all of you some of the "inside scoop" of how a conference is organized and run from the Co-Chairs' perspective. Many authors don't know what happens behind the scenes; and even most PC members don't get to chair a conference of this magnitude. We are honored to have been selected to co-chair USENIX ATC '20. Running a conference like ATC is substantially more work than some other, even well established conferences, for the reasons outlined below (and that effort skyrocketed when the pandemic hit). There is a lot to know and we hope that this information will be valuable to all of you in the future.

#### 2. Early Decisions

ATC is a large and complex conference to run for several reasons.

First, while it is a systems conference, ATC is fairly broad. Whereas conferences such as OSDI, FAST, NSDI, etc. see more focused papers, ATC has a much broader set of papers that span many systems conferences: networking, storage, operating systems, security, etc. This breadth meant that the PC's makeup had to be carefully balanced to ensure appropriate representation for all likely topics.

Second, ATC is also the place where new systems papers are often submitted for topics that may not have a home of their own. FAST, NSDI, USENIX Security, and others—all started in part because ATC was getting too many papers in those areas, suggesting it was time to form a new, more focused conference. In recent years ATC started getting papers on edge computing and applied machine learning; and this year we expected we might get for the first time ever papers in quantum computing (and we were right). This meant that the PC's makeup also had to include people who could review papers in newer and emerging topics such as machine learning and quantum computing.

Third, ATC receives submissions from many first time or relatively junior authors. Everyone has to start somewhere. But this meant that the PC had to do more work in reviewing and shepherding papers.

It would be nearly impossible to find ATC PC Chairs who are experts in all areas of systems research, including emerging ones. Recognizing this, we decided, for the first time, to recruit a few "PC Leaders" early on. We recruited five excellent PC leaders who, in addition to reviewing papers, would also help us form the PC itself. These five Leaders are experts in areas that us Co-Chairs were not as knowledgeable in, and they were instrumental in recommending and helping us pick members for this large PC.

Another important decision we made followed previous ATCs: we selected two "Submission Co-Chairs," one each at our respective institutions: Ketan Bhardwaj (Georgia Institute of Technology) and Dongyoon Lee (Stony Brook University). They were instrumental in assisting us run the conference submissions site (HotCRP) and overall, during the review process. They helped us analyze data, collect various statistics, write scripts, monitor online discussions, helped us run the (virtual) PC, and more. We cannot imagine running this conference without them, especially when the pandemic demanded a lot more effort on everyone's part.

#### 2.1. Decisions we made early on: R1 rejections, topics/themes

Every chair gets a chance to redefine the process of running the conference somewhat. We looked at past conferences as well as past ATCs and decided to try a few changes.

#### 2.1.1. Two review rounds and early rejections

ATC and other conferences have two rounds of reviewing. In the first round (R1), every paper gets a few reviews, and we decided to keep it at 3 reviews. There would then be online discussion and filtering. Those papers deemed worthy would advance to the second round of reviewing (R2) and receive about 2 more reviews. We aimed for 3 reviews in R1 and 5 in R2. There's an "art" of sorts to deciding how many reviews to have in each round: if you have too few, less informed decisions are made. But ironically, if you have too many reviews, in many cases that does not lead to better decisions. We have seen it before:

when you assign a paper more reviews, there's sometimes less convergence to an accept/reject decision; often the result is more variance, so converging on a decision is harder. No, more reviews aren't necessarily better. Rather, PC members have to be given time to discuss their reviews and try to convince each other of the merits of one's opinions.

Traditionally, papers that don't make it to R2 are slated for rejection. But as there's a second round of reviewing and a PC meeting, there's often a month or more between when R2 reviewing begins and all rejection notices are sent.

So we decided to send rejection notices for papers in R1 who didn't make it to R2, as quickly as we could. That was almost a month before final paper decisions were released. We did this to help authors, who now have even more time to consider their papers and the reviews they received, and decide how to revise the work for an eventual resubmission.

While sending R1 rejections helped authors, it meant more work for the PC and Co-Chairs, and a tighter schedule. Before any reviews are sent out, we decided to follow past models and perform a "Review Sufficiency Check" (RSC). In this stage, a paper reviewer is assigned to read all of the reviews and to ensure that they are complete, detailed, fair, respectful, proofread, and not missing useful information. An example of what an RSC check catches is when a reviewer might say "this work was done before," during this RSC phase, we would catch this and ask the reviewer to provide more details such as an actual citation to the "done before" work.

#### 2.1.2. Paper topics

When authors submit papers, they check several boxes to indicate what topics their paper fits into (e.g., networking, storage, operating systems). Similarly, before PC members begin to review any paper, they log in to the conference reviewing system, HotCRP (yes, pronounced hot-crap :-), and configure their expertise level in each of the topics. PC members mark their expertise on a five-point scale from "no expertise," to "neutral," to "expert." This indicates the PC member's preference in reviewing or not reviewing papers on certain topics.

Assigning hundreds of papers to over 100 PC members is a daunting task. Thankfully, HotCRP has a built-in "auto-assignment" feature. HotCRP can match papers to PC members by mutual interest in a given topic. HotCRP's initial assignment is very helpful but is not perfect, so it still needs a lot of review and tweaking by the Co-Chairs.

One trend in recent years has been to increase the number of topics and even add "cross-cutting" themes (sometimes called "aspects"). For example, instead of just saying "networking," you break it down into local-area, wide-area, mobile, protocols, data-center, etc., networking. And instead of saying "storage" you break it down to file systems, NVMs, Flash storage, network storage, KV stores, etc. And then you add orthogonal themes that can be applied to any of the finer-grained topics, for example: performance, scalability, security, availability, reliability, scheduling, etc.

There was a good reason to add more and more fine-grained topics and themes: HotCRP could do a better matching of papers to reviewers, ensuring that the best-qualified experts would get to review a paper. But there was a growing problem with the proliferation of topics and themes.

First, asking PC members and authors to mark 60+ topics and themes was a growing burden.

Second, authors don't always mark their papers correctly, often missing important topics/themes.

Third, some PC members don't want to mark their topic preference on purpose: they would like to get a "random assignment" of papers from the pool of submissions. There is a valid reason for this. A good paper should not just appeal to experts in the paper's field, but to a wider audience from the same community. So by reviewing some papers by highly technical PC members, but not necessarily experts, you ensure the selection of papers with greater appeal to the systems community.

Fourth, and most important. We found that the "cross-cutting themes" were not helping much; in fact, they were likely hurting HotCRP's initial assignment of papers to reviews. Suppose an author marks their paper with one or more topics and the theme of "performance." A person who can review a "storage performance" paper well probably won't be able to review a "network performance" paper as well. Similarly, "scheduling" in data centers is very different from I/O scheduling or network-packet scheduling. Analyzing these themes, we decided that they were not helpful and even counter-productive, and so we decided to eliminate all cross-cutting themes from the USENIX ATC '20 CFP.

Next, we tackled proliferation in the number of themes. After much discussion that involved our PC Leaders and Submission Co-Chairs, we decided to narrow the list of topics from several dozen to just 14. The reason to reduce the number of topics was to lower the burden on authors and PC members when marking their expertise; but at the same time, we wanted to ensure that we would still be able to assign papers to expert reviewers. So we chose multi-topic themes such that expertise in one

topic is likely to translate to another. For example, one topic was "Distributed Systems, Clouds, Clusters, Data Centers." The idea was that if a PC member can review a paper in "Distributed systems," then they should also be able to review a paper on "data centers" reasonably well. No paper-to-reviewers assignment is ever perfect, but we felt that the way we chose themes and fewer of them helped reduce overall burden and still keep the reviewing quality high.

#### 3. PC Selection Process

PC selection is a multi-dimensional optimization problem. Co-Chairs have to ensure that the PC is well balanced as much as possible across multiple dimensions (in no particular order):

- 1. Junior vs. senior people: it's good to have some "fresh blood" and first time PC members, but also to have senior people who provide the necessary "institutional memory" and the wisdom that comes with... gray hair.

- 2. Industry vs. academia: it's not enough to have just academics on a PC. We have to have representation from industry, who work on many real-world cutting-edge problems.

- 3. Domestic vs. international: the systems community is spread around the world. We want representation not just from U.S. researchers, but from Europe, Far and Middle East, and more.

- 4. Male vs. female: notwithstanding that genders are not binary, computer science and systems research are sorely lacking in female representation. This is true in academia (faculty and students), as well as industry. Inclusivity and diversity has proven to improve outcomes of many decision-making processes. Alas, our community has far fewer female researchers than we'd like to have. Many female researchers get asked repeatedly to serve on PCs, creating perhaps an unfair load. We tried to invite as many female PC members to join as we could: 24% of invited were female; and in the end our PC had 23% female representation.

- **5. Topic diversity:** it's important for the PC to have just the right number of people to review papers in various topics. We reviewed stats from previous years, such as how many papers were received in traditional topics (e.g., storage, clouds) as well as emerging topics (e.g., edge, ML). We estimated how many papers we might get overall and how many papers in each topic. We planned for getting anywhere from 300 to 500 (worst case) submissions. In the end, we had just under 350 reviewed submissions. For each PC member we considered inviting, we had a spreadsheet to mark their expertise in various areas.

Next, we chose to follow previous year's models and invite PC members in multiple rounds and for multiple effort levels. During the fall of 2019 we sent out eight different rounds of invitations. After waiting to hear back, we reviewed the current makeup of the PC along the five aforementioned dimensions. We used google sheets and docs extensively. We then adjusted our strategy and sent out the next round of invitations, consulting with our PC Leaders as necessary. Adjustment was necessary to ensure that, if we were short in one dimension above, that we doubled our efforts to catch up along that dimension without hurting other dimensions.

We offered three tiers of reviewing load. Heavy PC members were expected to review 16-20 papers; Light PC members were expected to review 8-10 papers; and External Review Committee (ERC) members were expected to review 1-3 papers at most. Heavy PC members were required to attend the physical PC meeting (which was converted to a virtual PC-more on that later). ERC members were selected for specialized expertise in narrow areas where we felt we would need a couple more reviews. All PC members were expected to review papers in two rounds and participate in both rounds' online discussions. We first invited Heavy, then Light, then ERC. In some cases, those who declined our invitation to be Heavy PC members were offered to be a Light PC member (several agreed).

We made a total of 214 PC invitations. 42% of all invited declined (many are understandably busy). Of the 125 that accepted, we had 67 Heavy PC members, 48 Light, and 10 ERC.

CFP updated and posted, PC formed, HotCRP configured, we were ready...

... or so we thought.

Con permiso, Capitán. The hall is rented, the orchestra engaged. It's now time to see if you can dance. -Q to Captain Picard, "Q Who," Star Trek: The Next Generation

#### 4. Before Paper Submission Due Date

Anonymizing papers helps ensure the integrity of the conference. When neither authors nor PC members know each other's identity, this is called a double-blind review process.

We received dozens of emails from authors who asked for clarifications on how to anonymize their papers. This is always a difficult subject. If you anonymize your paper too much, you may be hiding information about useful prior work you did, which could help the current paper under submission. Ironically, if you anonymize your past work too well, you could be incorrectly accused of reproducing or even plagiarizing "someone else's work" where it's really your own work.

If you don't anonymize, or poorly anonymize, you expose your identity, even indirectly to PC members. There's no consensus whether it helps or hurts a paper's chances, but there is consensus that it biases the process one way or another.

Many ATC authors are first-timers or relatively junior, which explains why we received many such queries about the anonymization process. Our advice to authors was as follows. PC members are encouraged not to search the Internet for information that might reveal the authors' identities. So authors had to ensure that their papers were anonymized and self-contained. Citations to one's own paper should be stated in the third person: you can refer to your own past work as "John Doe et al. [1] did this or that" and then state how you improved on those "other" people's work.

There are times when anonymization can get very difficult. Suppose the authors are from a very large cloud operator and are reporting on their experiences running a million computers across dozens of data centers worldwide. This kind of experience is invaluable to report to the systems community, as most researches can only dream of having access to such a large set of computers and its associated data sets. Therefore it doesn't make sense in such a paper, to "hide" details as to the size and scope of the environment being studied: hiding such details would likely hurt such a paper considerably. However, anyone reviewing such an anonymized paper would have a pretty good guess which company the authors work for. After all, we can all count on one hand the number of cloud operators with such a large operation.

The above was just one example. We generally told authors that anonymizing is a "best-effort" process: try your best to hide your identity but avoid going too far that it genuinely hurts your paper.

#### 5. After Submissions Were Received

HotCRP had 408 records of submissions, but many were just from novice authors experimenting with HotCRP to see how it works; some authors re-uploaded their paper multiple times, creating duplicate submissions; and some authors registered the paper days earlier, but withdrew or never completed their submission.

There were just over 350 complete submissions. We inspected each one of them! Not surprisingly, we found over a dozen submissions that did not follow the rules: many did not anonymize and even had the authors' full names on the title page; some had bad fonts or bad PDFs; some had odd background colors or a watermark; some violated the formatting guidelines (fonts, sizes, margins, or the number of pages). We contacted each of those papers' authors and gave them 24 hours to fix their submission or we might have been forced to withdraw their papers. Most authors complied quickly. A couple of papers were withdrawn. We were left with 348 submissions that were ready to be reviewed.

#### 6. Conflict Management and Integrity

A conference's reputation and prestige depend heavily on at least two important factors. First, the number, length, and quality of the reviews received. This is especially important for rejected papers. Getting a paper rejected is always disappointing; a good conference will provide reviews that would show authors that reviewers understood their paper, read it carefully, and provided constructive criticism to help the authors improve the work for a future resubmission.

Second, the perceived fairness of the process. In a conference like ATC, where over 80% of all papers are rejected, it is vital that the authors of all those rejected papers would feel that the process was fair and unbiased: that the decision on papers which got accepted or rejected was based on merit alone, and not on who reviewed, who was on the PC, or who are the conference organizers.

In 2019, there were stories circulating about possible poor practices in certain systems conferences. In one case this led to a tragedy. Organizations such as ACM and IEEE are still investigating various reports. And we have also heard from other senior members of our community, directly and indirectly, about possible conflicts and violations of anonymity rules.

We expected and followed three common conflict and anonymity rules:

- 1. PC chairs are prohibited from submitting papers to their conference. When recruiting our Submission Co-Chairs, we told them they would also not be allowed to submit papers to ATC'20. That is because all four of us had "superuser" privileges on HotCRP, allowing us to see any review.

- 2. Authors had to mark every PC conflict (and select a reason) for their paper. HotCRP is excellent at ensuring that conflicted PC members had no direct or indirect knowledge about papers those PC members are conflicted with: they can't see reviews, who reviewed, or scores; and they would be excluded from all online and PC discussions regarding conflicted papers.

- 3. Both of us Co-Chairs had papers marked as conflicts (often from our collaborators or ex-students). That's unavoidable. Thankfully there were no papers in which we were both conflicted. Therefore, we decided that each one of us PC Co-Chairs would alone handle all matters (e.g., PC discussions and decisions) relating to papers we were conflicted on; this included getting us PC Co-Chairs (or Submission Co-Chairs) excluded from parts of the live PC meeting discussions, as well as the selection of paper awards.

Nevertheless, we decided to "take it up a notch":

First, we added a new statement to the CFP that read as follows:

Authors and others are prohibited from directly or indirectly communicating with any ATC '20 PC/ERC member about any potentially submitted paper. All requests should be made exclusively to atc20chairs@usenix.org. Violations of these guidelines may seek remedies as stipulated in the USENIX Conference Submissions Policy.

This was to ensure that PC members and authors should never communicate directly, regardless of whether a paper was accepted or rejected, even after the conference is long passed.

Second, our Submission Co-Chairs leveraged past scripts and data-sets that scour the Web, DLBP paper databases, and other resources. Those scripts attempt to identify additional or incorrectly marked conflicts for every paper. The scripts, for example, attempt to find if person A collaborated with person B on a recently published paper, person A submitted to USENIX ATC '20, person B was a PC member, but person B was not marked as a conflict for person A's submission. The scripts also looked at possible institutional conflicts, and more.

These scripts were far from perfect. They produced many false positives due to very similar names as well as their inability to perfectly match people's names with abbreviated initials. Our Submission Co-Chairs manually poured over thousands(!) of flagged potential conflicts from these scripts and together we narrowed them down to about 242 possible conflicts across 92 papers. We wrote separate scripts that emailed all authors and asked them to verify whether these possible conflicts were valid or not. Over 50% of all responses indicated that indeed these were valid conflicts for those papers, and so we marked additional conflicts.

We were now ready in earnest to assign papers to reviewers and begin the first round of reviews.

Phew.

#### 7. Next Stages of Running a Conference

At this stage of any conference, about half of the Co-Chairs' work is done: forming a PC, posting a CFP, getting and sanitizing papers, and assigning reviews. We could now sit back and relax for a while...

... or so we thought.

COVID-19 happened. In other words, the Borg was unleashed on us before anyone was ready.

For many of us, the amount of work in our day-jobs increased considerably. Food and supply shortages. Dire predictions every day. No one knows what happens next. Many of us who are parents were having to juggle twice the workload and now having to provide full-time childcare, with schools and childcare facilities closed. People losing their jobs in droves. The economy tanking. The stress levels everyone was going through were through the roof.

We began to receive reports from PC members who were unable to meet the already tight review deadlines. Some reviewers reported stress, work and family problems, and even health problems related to COVID-19. Not prying, we tried our best to work with everyone's abilities and schedules. In some cases, we had to reassign papers and reviews to ensure we kept the expected review quality of ATC. This was a non-stop daily effort from mid-February to mid-April of 2020.

#### 8. The PC Meeting

An in-person PC meeting is important. No amount of written reviews and numeric scores can replace the human experience. When people discuss a paper face to face, everyone can better gauge exactly how every reviewer feels about a paper. Seeing people's faces, hearing the inflection in their voices, and noting their body language are all vital cues that help us communicate better with one another. This is especially important because the PC meeting is often reserved for the most challenging borderline papers whose fate depends on informed discussions.

We had grand plans to hold a day-long physical PC meeting at Georgia Tech. The plan was to review no more than 70 papers during the PC meeting.

We started to get many emails from PC members who were concerned about traveling due to their own health, or their employer restricted or prohibited all travel. It was clear that holding a physical conference was not possible. So we canceled it and informed all PC members that it would be a virtual PC.

We had no idea how we would run a virtual PC yet. But we realized that we would not be able to hold a day-long virtual PC, nor would we have time to review ~70 papers virtually.

Based on past experience, we had already decided to pre-accept and pre-reject some papers during the R2 discussion period (and recall we also sent out early rejections for papers that were rejected in R1). The thinking was that if the PC can reach accept/reject decisions on some papers during the R2 online discussion period, and ahead of the PC meeting, then there would be fewer papers that had to be discussed at the actual PC. Past experience suggested that such papers' decisions rarely change during a PC meeting, so it was just going to waste time if we discussed them. Therefore, we assigned a discussion leader to each paper and asked them to see if a consensus could be reached during the R2 discussion period: pre-accept, prereject, or "need to be discussed at the PC." We gave PC members wide latitude to opine on those pre-accepted and prerejected papers. If any reviewer felt the decision was incorrect, then that paper would be discussed at the PC instead.

In normal times, it's just too easy to "punt" on making difficult decisions and merely push the paper to be discussed at the PC meeting. But now, having been forced to run a shorter, virtual PC, we could not afford to leave too many papers for the PC meeting itself. So we pushed our PC to make the difficult decisions early on, try to reach consensus, and pre-accept or pre-reject as many papers as possible. In order to provide for some cross-paper "calibration," we configured HotCRP so as to make all reviews and discussions visible to all non-conflicted PC members. This was difficult for everyone, especially during a worldwide pandemic. But our PC did admirably well. We were left with 38 papers to discuss at the PC meeting.

#### 8.1. The Virtual PC (vPC)

Running a virtual PC (vPC) was a new thing. Few have ever attempted it. We could write ten more pages of "Chair Notes" about our experience. Wait, we did! You can find our full-length report on how we planned and ran our vPC here: https://www3.cs.stonybrook.edu/~ezk/vPC.html. So we'll only give you the highlights below:

- 1. We (two Co-Chairs and two Submission Chairs) evaluated multiple solutions and in the end, we chose Zoom as the most suitable one.

- 2. We shortened the PC meeting to just five hours. But we underestimated how long it would take. Indeed, we ran about 2 hours longer.

- 3. We polled our PC members for their schedules and current time-zones. And we clustered the papers to discuss into groups that best optimize for PC members' availability.

- 4. In a physical PC meeting, PC members who are conflicted are asked to leave the room, then they're called back in. With a vPC, we used Zoom's "Waiting Room" feature: it neatly allowed us to virtually move conflicted PC members from the actual PC to the waiting room, where their video and audio are disabled, they cannot hear or see any of the discussions, until they are let back in.

Given the unprecedented circumstances we faced, we believe the vPC went very well. And we strongly believe that USENIX ATC '20 maintains the high standards of quality despite all that everyone had to go through.

#### 8.2. The Stats

And now, for the customary statistics from the paper review process.

Finalizing the program decisions for USENIX ATC '20 took 1,379 reviews, 4,193 discussion comments posted during the two online discussion rounds (post R1 and post rebuttals). The PC wrote a total of over 1.15 million words. Out of the initial 348 submissions, 150 papers (43%) were advanced to the second round, the remaining 198 papers received an early (R1) rejection notification. During the post-rebuttal online discussion period, the PC decided to pre-accept 42 highly-ranked papers and to pre-reject 70 more papers. The remaining 38 papers were further discussed during the vPC meeting. 23 of these papers were accepted and 15 were rejected. The final acceptance rate for ATC '20 is 18.7% (65 out of 348).

Among the accepted papers, 61 are regular full-length papers, 3 are short papers which were submitted as short, one paper will appear at the conference as a short paper but was originally submitted as a full-length 11-page paper, and another paper submitted as long was accepted as a short paper but given 9 pages. All accepted papers were initially conditionally accepted and assigned 1 or 2 shepherds, who ensured that the final version of the paper addressed the reviewers' feedback.

#### 9. The Conference

With the paper selection process complete, we were almost done—just to organize the papers in sessions that fit the more-orless standard schedule template that USENIX was going to provide...

... or so we thought.

Shortly after the vPC concluded and all decisions were communicated, unsurprisingly, it was determined that the actual conference will also have to be held as a virtual event. So, we were back in uncharted territory, trying to make the best decisions on how to organize and run a multi-day, multi-track USENIX ATC '20 conference—and for the first time fully online.

We spoke with Co-Chairs of other major systems conferences that switched to virtual mode—ASPLOS '20, Eurosys '20, and ISCA '20. We polled some of our PC members for their feedback from virtual conferences they had attended. We read blogs and recommendations on different virtual conference tools and experiences. We consulted on a weekly basis with the USENIX staff and the Co-Chairs of the workshops affiliated with ATC (HotStorage and HotCloud). And we mapped out the time zones of the authors of the accepted papers, and much more.

In the end, we arrived at a program that retained the original conference dates, organized in 12 technical papers sessions presented in two parallel tracks, and two plenary keynote addresses. With a goal of creating a balance among giving to authors an opportunity to present their work in front of a live audience, providing conference attendees with high-quality technical content, and shielding everyone from "Zoom fatigue," we opted for a schedule that combines longer, asynchronously-delivered, pre-recorded presentations, and live sessions with shorter video presentations and Q&A.

The two keynotes are scheduled at the end of the first two days of the conference, with ample time for discussions and Q&A. The first keynote is by Professor Ethan Miller from UC Santa Cruz on "The Future of the Past: Challenges in Archival Storage" and discusses, for example, future storage technologies such as DNA and Glass. The second keynote is by Professor Margo Seltzer from the University of British Columbia, titled "The Fine Line between Bold and Fringe Lunatic." Margo's talk hopefully sets a new tradition at USENIX ATC where the previous year's Lifetime Achievement Award Winner delivers one of the keynote addresses in the following year.

We look forward to three days of technical papers, keynote presentations, and discussions.

#### 10. In Closing

Despite the tremendous amount of (unanticipated) work, we are thrilled to have had the honor of chairing USENIX ATC. We are thankful to everyone who helped and contributed along the way: to the authors who submitted their high-quality work to ATC, to the dedicated program committee and external reviewers who evaluated hundreds of submissions and provided constructive feedback to the authors, to the PC Leaders, Submission Co-Chairs and to the USENIX staff who provided invaluable advice and support.

We are excited to welcome everyone at the first-ever virtual USENIX Annual Technical Conference, and we hope you will enjoy it.

USENIX ATC '20 Program Co-Chairs Erez Zadok, *Stony Brook University* Ada Gavrilovska, *Georgia Institute of Technology*

## Libnvmmio: Reconstructing Software IO Path with Failure-Atomic Memory-Mapped Interface

Jungsik Choi

Sungkyunkwan University

Jaewan Hong KAIST Youngjin Kwon KAIST

Hwansoo Han Sungkyunkwan University

#### **Abstract**

Fast non-volatile memory (NVM) technology changes the landscape of file systems. A series of research efforts to overcome the traditional file system designs that limit NVM performance. This research has proposed NVM-optimized file systems to leverage the favorable features of byte-addressability, low-latency, and high scalability. The work tailors the file system stack to reduce the software overhead in using fast NVM. As a further step, NVM IO systems use the memory-mapped interface to fully capture the performance of NVM. However, the memory-mapped interface makes it difficult to manage the consistency semantics of NVM, as application developers need to consider the low-level details. In this work, we propose Libnymmio, an extended user-level memory-mapped IO, which provides failure-atomicity and frees developers from the crash-consistency headaches. Libnymmio reconstructs a common data IO path with memory-mapped IO, providing better performance and scalability than the state-of-the-art NVM file systems. On a number of microbenchmarks, Libnvmmio gains up to  $2.2\times$  better throughput and  $13\times$  better scalability than file accesses via system calls to underlying file systems. For SQLite, Libnvmmio improves the performance of Mobibench and TPC-C by up to 93% and 27%, respectively. For MongoDB, it gains up to 42% throughput increase on write-intensive YCSB workloads.

#### 1 Introduction

The recent surge of non-volatile main memory (NVM) technology such as PCM [32, 55], STT-MRAM [4, 30], NVDIMMs [45], and 3D Xpoint memory [21] allows applications to access persistent data via CPU load/store instructions directly. With the benefits of competitive performance, low power consumption, and high scalability, they are expected to complement or even replace DRAM in future systems [30, 33].

To leverage the performance and persistent features, researchers have proposed NVM-optimized file systems [8, 12,

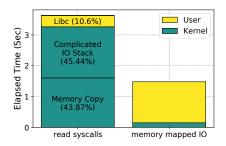

13, 24, 28, 46, 65, 67, 68]. The most important challenge addressed in the series of work is to revise the inefficient behavior of the software IO stack, which presents a dominating overhead in fast NVM [2, 3, 9, 22, 26, 48, 69]. To reduce the overhead, state-of-the-art NVM-aware file systems discard the traditional block layer and the page cache layer in the IO path. Despite these optimizations, file accesses through the OS kernel's file system still incur significant overhead. For example, read and write system calls are still expensive ways to leverage the low latency of NVM, due to frequent user/kernel mode switches, data copies, and complicated VFS layers [7,9,24,25,27,57,62].

A promising approach to further reduces IO overhead of NVM file systems is to use memory-mapped IO [9, 35, 58, 60, 67, 68]. The memory-mapped IO naturally fits the characteristics of NVM. Applications can map files to their virtual address space and access files directly with load/store instructions without kernel interventions. Memory-mapped IO also minimizes the CPU overhead of file system operations by eliminating file operations such as indexing to locate data blocks and checking permissions [65]. With these benefits, the mmap would be a critical interface for file IO in future NVM systems.

While memory-mapped IO exposes the raw performance of NVM to applications, a lot of responsibility is laid on applications as well. One thing to keep in mind for application programmers is that memory-mapped IO does not guarantee atomic-durability. If a system failure occurs during memory-mapped IO, the file contents may be corrupted and inconsistent in the application context. In return for fast performance, developers should build application-specific crash-safe mechanisms. Cache lines should be flushed to ensure durability and memory barriers should be enforced to provide a correct persistent ordering for NVM updates. This mechanism often induces a serious software overhead, and makes it notoriously difficult to write accurate and efficient crash-proof code for NVM systems [38, 50–52, 71]. For an instance, applying cache flush and memory barrier instructions correctly in the

right locations is challenging; excessive use causes performance degradation, but omitting them in required locations leads to data corruption [39, 70]. This is the major obstacle blocking the adoption of memory-mapped IO to fully exploit the advantages of NVM.

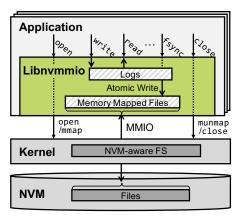

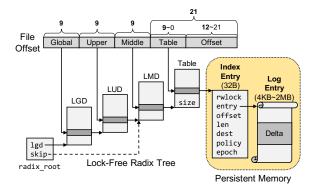

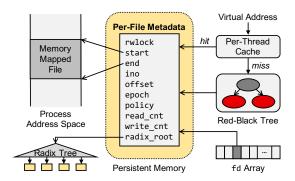

We propose *Libnvmmio*, a user library that provides failureatomic memory-mapped IO with msync. We add atomicity and ordering features to the existing msync at user-level. By separating failure-atomicity concerns from memory-mapped IO applications, Libnvmmio allows developers to focus on the main logic of programs. To make the msync failure-atomic, Libnvmmio uses user-level logging techniques. Our library stages written data to per-block, persistent logs and applies the updates to memory-mapped files in a failure-atomic manner on msync.

Implementing msync at user-level has many advantages. First, the user-level msync minimizes system call overhead. Existing msync imposes system call overhead, which takes locks and excessively serializes threads in a multi-threaded application. Second, it reduces write amplification. Kernel-level msync flushes rather large ranges whose size are multiples of the system page size (4KB, 2MB, or 1GB). Whereas, user-level msync can track dirty data at a cacheline granularity and flush them at cacheline level. Third, it avoids TLB-shootdown overhead. When applications invoke msync on NVM file systems, operating systems track down updated pages by searching for dirty bits in the page table and flush corresponding cache lines of those dirty pages to NVM. After the flush, they clear the dirty bits in the page table to enable tracking new updates. This incurs TLB invalidations in other cores, as dirty bit state is just kind of information in TLB along with the virtual to physical page mapping. As Libnvmmio's msync maintains user-level logs for update tracking, we can totally avoid TLB-shootdown overhead. Fourth, it takes advantage of non-temporal store instructions which bypass CPU caches with no need of cache flushing. Kernel-level msync flushes the entire range, even if updates are performed with non-terminal store instructions. In general, there is no other way to communicate with msync that the non-temporal stores are used. For all of these reasons, a user-level msync in Libnvmmio can perform better than a kernel-level msync.