# **EXILINX**ALL PROGRAMMABLE

## Achieving 10Gbps Line-rate Key-value Stores with FPGAs

Michaela Blott, Kimon Karras, Ling Liu, Kees Vissers - Xilinx Research Jeremia Baer, Zsolt Istvan - ETH Zurich

© Copyright 2013 Xilinx

#### Introduction

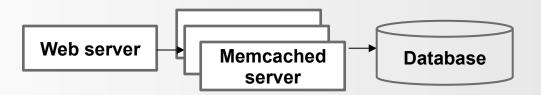

Common middleware application running on x86s to alleviate bottlenecks on databases

#### > Agenda

- State of the art

- FPGAs

- Proposed architecture

- Results

- Limitations

## **Typical Memcached Implementations**

#### > Best published numbers:

| Platform                                                    | RPS [M] | Latency [us]  | RPS/W [K] |    |

|-------------------------------------------------------------|---------|---------------|-----------|----|

| Intel Xeon (8 cores)                                        | 1.34    | 200-300       | 7         | 7K |

| Intel Xeon (2 sockete (asores)                              | 3.15    | 200-300       | 11.2      |    |

| Memcache <b>1.4MRPS</b> d & Intel Xeon (2 sockets, 16cores) | 1.8     | 12 200us late |           |    |

| TilePRO (64 cores)                                          | 0.34    | 200-400       | 5.0       |    |

| TilePRO (4x64 cores)                                        | 1.34    | 200-400       | 5.8       |    |

| Chalamalasetti (FPGA)                                       | 0.27    | 2.4-12        | 30.04     |    |

Source: see paper

#### XILINX > ALL PROGRAMMABLE..

#### What are FPGAs?

Semiconductor devices that consist of a matrix of configurable logic blocks (CLBs) connected via programmable interconnects.

- > On an extremely large scale highly integrated (28nm, 2million logic cells)

- > Nowadays, FPGAs integrate many other blocks

- Up to 3600 DSPs, 68Mb SRAM, 96 high-speed serial IO, ARM processors (Cortex-A9)

- > They can be programmed to become ANY custom circuit

- Ideal for architectural exploration

#### We use FPGAs to implement a new dataflow-based architecture for memcached

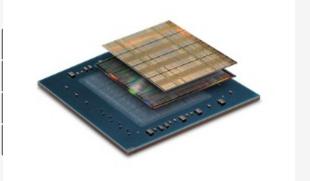

## **Programming FPGAs?**

FPGAs can be reprogrammed after manufacturing through hardwarebased design flow

Hardware design exposes a greater complexity to the user and requires therefore more engineering effort

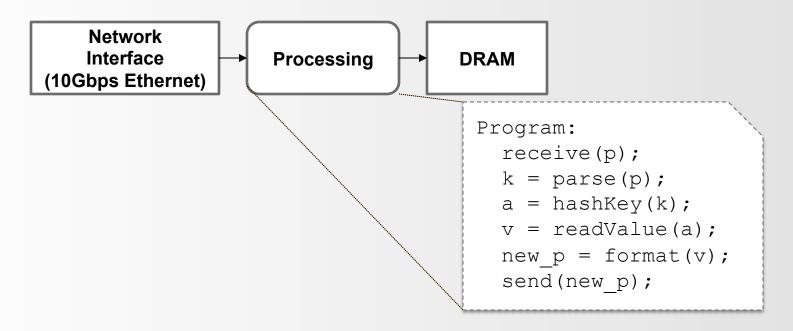

## Why Dataflow Architectures?

- > Memcached is fundamentally a streaming problem

- Data is moved from network to memory and back with little compute

Dataflow architectures, frequently used for network processing, should be well suited towards the application

🗶 XII INX 🔰 ALL PROGRAMMABLE.

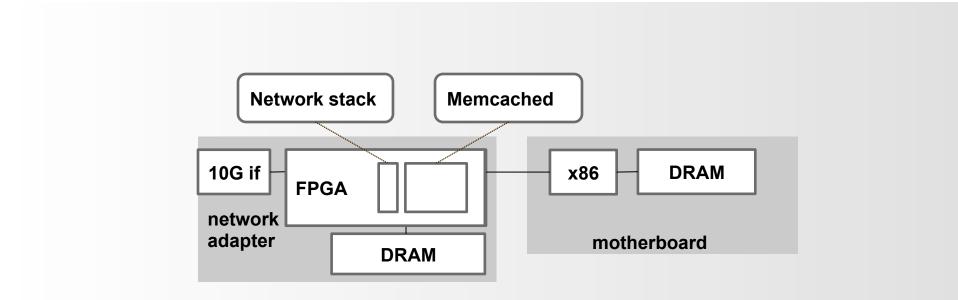

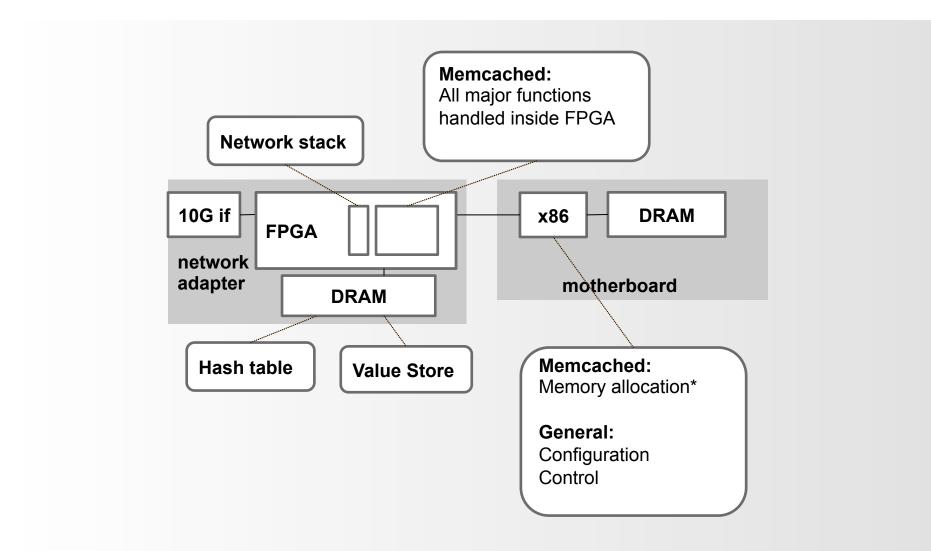

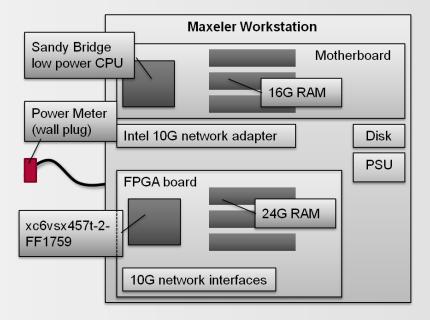

## **System-level Architecture**

> High throughput through data-flow architecture

- > Low latency through tight integration of network, compute and memory

- > Hash table to support 2 million entries and 24GB of storage

🗶 XILINX 🕨 ALL PROGRAMMABLE.

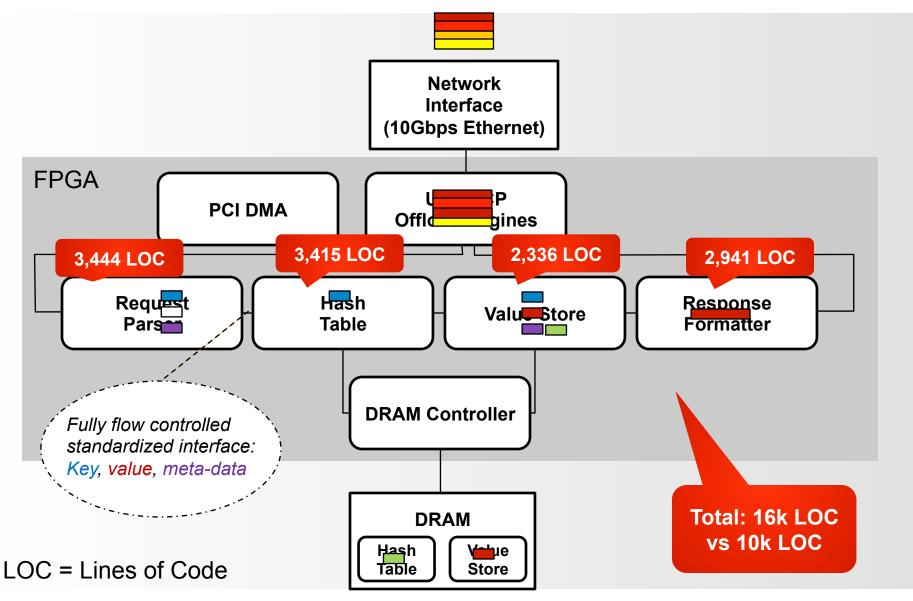

### **FPGA-based Dataflow Architecture**

© Copyright 2013 Xilinx

XILINX > ALL PROGRAMMABLE...

#### **FPGA-based Dataflow Architecture**

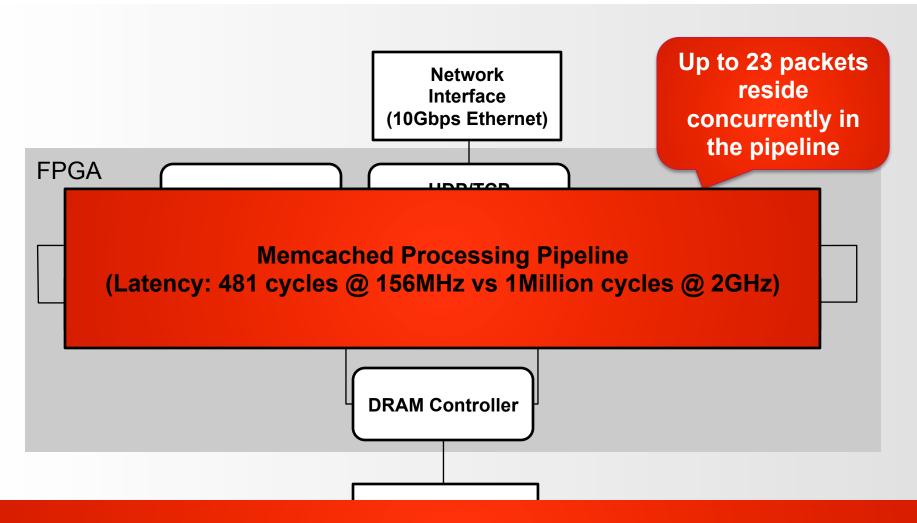

Exploiting task and instruction-level parallelism increases throughput and is more power efficient Inherently scalable

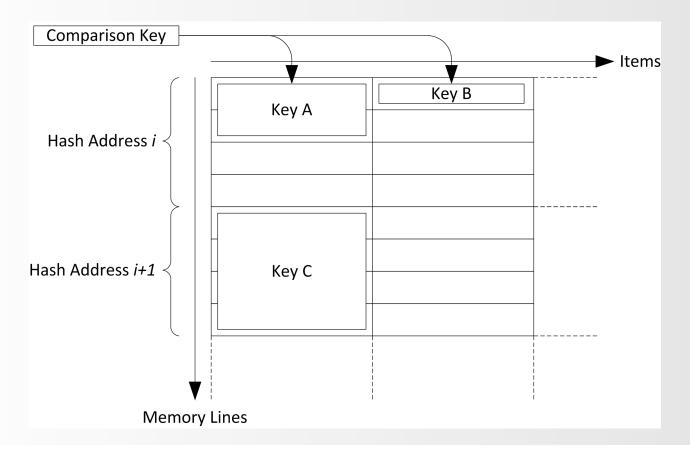

#### Hash Table architecture

- > Bob Jenkins lookup3 implemented in FPGA

- Collision handling through parallel lookup (8-way)

- > Flexible key handling through striping

### **System-Level Architecture**

\*below 3% of 1 core for 10% SET operations \*limited memory access bandwidth on platform

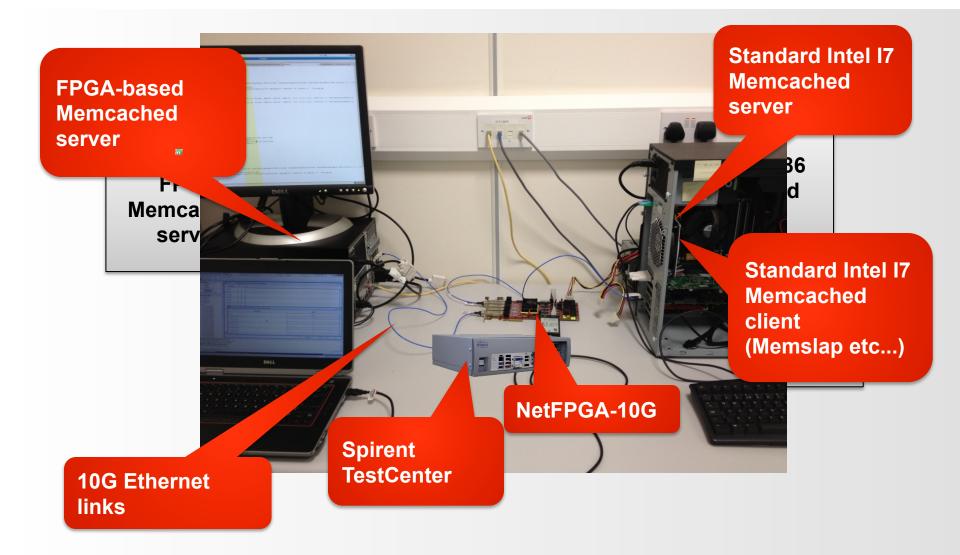

### **System Test Setup**

XILINX > ALL PROGRAMMABLE.

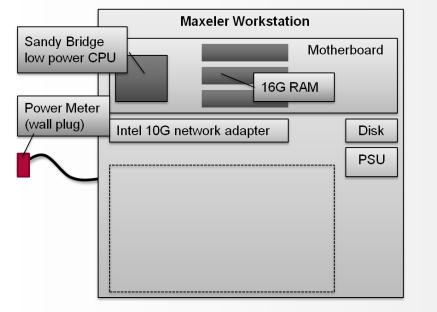

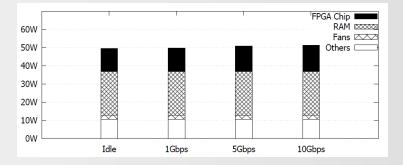

### **Power - Test Setup & Results**

#### Test system 1: without FPGA board

#### Test system 2: with FPGA board

XII INX > ALL PROGRAMMABLE.

\*(Power sourced from: power plug meter, xpower, data sheets and power regulator readings)

\*\*(UDP, binary protocol)

\*\*\*(includes FPGA and host system)

© Copyright 2013 Xilinx

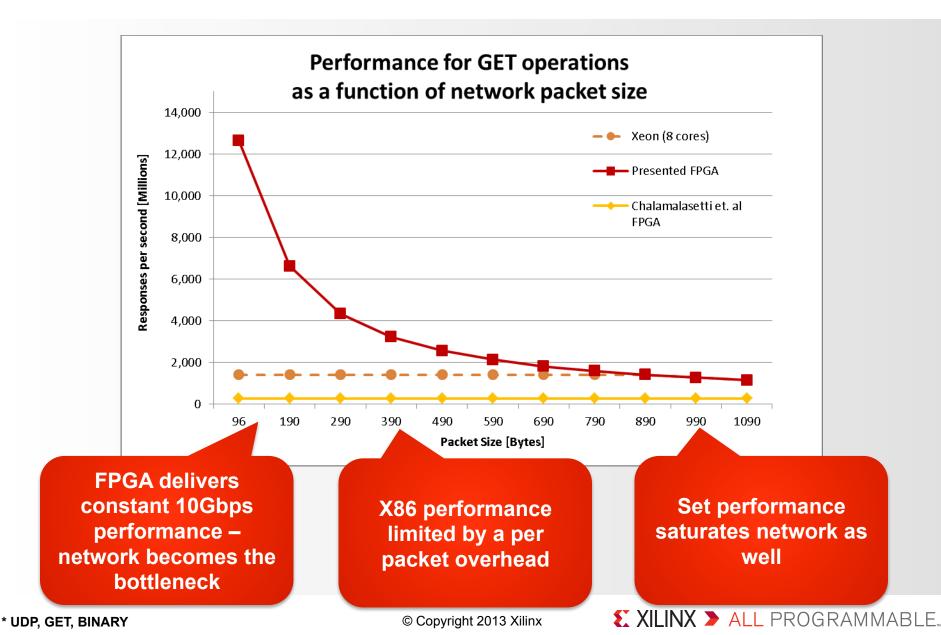

#### **Results - Performance**

## **First Results of Memcached Evaluation**

- > Sustained line rate processing for 10GE 13MTps possible

- Significant improvement over latest x86 numbers

- Lower power

- > Combined: 36x in RPS/Watt with low variation

#### > Cutting edge latency

microseconds instead of 100s of microseconds

| RPS [M] | Latency [us]        | RPS/W [K]                                                         |  |

|---------|---------------------|-------------------------------------------------------------------|--|

| 1.34    | 200-300             | 7                                                                 |  |

| 0.34    | 200-400             | 3.6                                                               |  |

| 13.02   | 3.5-4.5             | 254.8                                                             |  |

| 13.02   | 3.5-4.5             | 106.7                                                             |  |

|         | 1.34   0.34   13.02 | 1.34   200-300   I     0.34   200-400   I     13.02   3.5-4.5   I |  |

Source: see paper

#### XILINX ➤ ALL PROGRAMMABLE.

## **Current Platform Limitations**

- Memory allocation & cache management

- Current platform limitation

- Limited protocol support

XII INX > ALL PROGRAMMABLE.

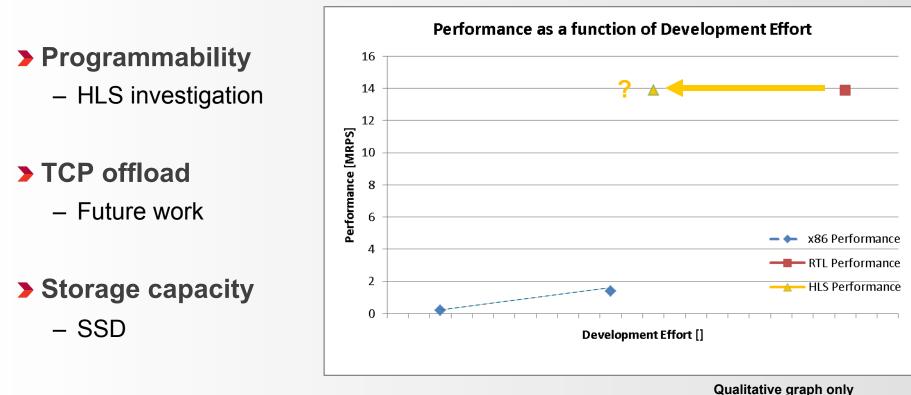

## **Summary & Next Steps**

- Dataflow architecture delivers 10Gbps line-rate performance and scalability to higher rates

- Significantly higher RPS/Watt, with that lower TCO

> Minimal latency

#### > Next Steps:

- Addressing limitations

- Trials with real use cases

- Exploration of other applications

# **EXILINX**ALL PROGRAMMABLE

## Thank You. mblott@xilinx.com