# conference

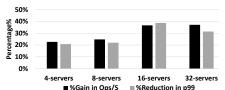

proceedings

gs of the 2019 USENIX Annual Technical Conference

# 2019 USENIX Annual Technical Conference

Renton, WA, USA July 10–12, 2019

Sponsored by

# **USENIX ATC '19 Sponsors**

**Gold Sponsors**

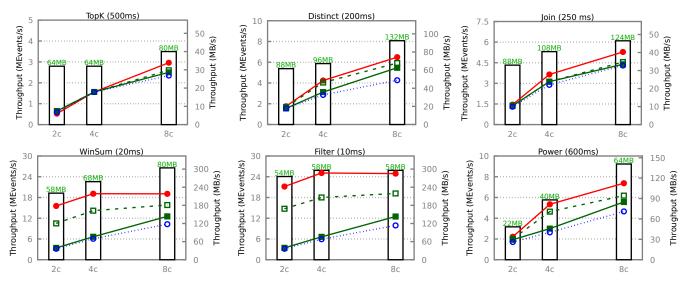

**Silver Sponsor**

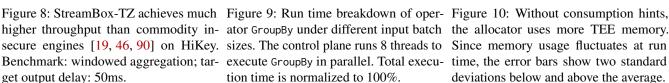

**Bronze Sponsors**

# **USENIX Supporters**

# **USENIX Patrons**

Bloomberg • Facebook • Google Microsoft • NetApp

# **USENIX Benefactors**

Amazon • Oracle • Two Sigma • VMware

# **USENIX Partners**

Cisco Meraki • ProPrivacy • Restore Privacy Teradactyl • TheBestVPN.com

**Open Access Publishing Partner**PeerJ

# **USENIX** Association

# Proceedings of the 2019 USENIX Annual Technical Conference

July 10–12, 2019 Renton, WA, USA

#### © 2019 by The USENIX Association

All Rights Reserved

This volume is published as a collective work. Rights to individual papers remain with the author or the author's employer. Permission is granted for the noncommercial reproduction of the complete work for educational or research purposes. Permission is granted to print, primarily for one person's exclusive use, a single copy of these Proceedings. USENIX acknowledges all trademarks herein.

## **Conference Organizers**

**Program Co-Chairs**

Dahlia Malkhi, VMware Research

Dan Tsafrir, Technion—Israel Institute of Technology & VMware Research

**Program Committee**

Nitin Agrawal, *ThoughtSpot* Irfan Ahmad, *Magnition* Deniz Altinbuken, *Google*

Nadav Amit, VMware Research Group Saurabh Bagchi, Purdue University

Mahesh Balakrishnan, Yale University and Facebook Antonio Barbalace, Stevens Institute of Technology Andrew Baumann, Microsoft Research Redmond Adam Belay, Massachusetts Institute of Technology

Ken Birman, Cornell University Edward Bortnikov, Yahoo

Herbert Bos, Vrije Universiteit Amsterdam

Andre Brinkmann, Johannes Gutenberg-University Mainz

Edouard Bugnion, École Polytechnique Fédérale de Lausanne (EPFL)

Randal Burns, *Johns Hopkins University*Anton Burtsev, *University of California, Irvine*Haibo Chen, *Shanghai Jiao Tong University*

Vijay Chidambaram, The University of Texas at Austin and VMware Research

Asaf Cidon, Barracuda Networks

Austin Clements, Google David Cock, ETH Zurich

Paolo Costa, Microsoft Research John Criswell, University of Rochester

Charlie Curtsinger, *Grinnell College* Dilma Da Silva, *Texas A&M University*

Nathan Dautenhahn, Rice University Eyal de Lara, University of Toronto

Christina Delimitrou, Cornell University

Angela Demke Brown, University of Toronto

Fred Douglis, *Perspecta Labs* Eric Eide, *University of Utah*

Michael Factor, *IBM Research—Haifa* Pascal Felber, *University of Neuchâtel*

Christof Fetzer, TU Dresden

Moshe Gabel, University of Toronto

Ada Gavrilovska, Georgia Institute of Technology Phillip Gibbons, Carnegie Mellon University Cristiano Giuffrida, Vrije Universiteit Amsterdam

Ashvin Goel, *University of Toronto* Boris Grot, *University of Edinburgh*  Steven Hand, Google

Liting Hu, Florida International University

Yu Hua, Huazhong University of Science and Technology Jian Huang, University of Illinois at Urbana-Champaign

Bill Jannen, Williams College

Sudarsun Kannan, Rutgers University Manos Kapritsos, University of Michigan Kimberly Keeton, Hewlett Packard Labs Samira Khan, University of Virginia

Taesoo Kim, Georgia Institute of Technology Sam King, University of California, Davis

Aasheesh Kolli, *The Pennsylvania State University* Dejan Kostic, *KTH Royal Institute of Technology*

Geoff Kuenning, Harvey Mudd College

Patrick P.C. Lee, The Chinese University of Hong Kong

Xing Lin, NetApp

Ethan Miller, *University of California*, *Santa Cruz*, and *Pure Storage*

Changwoo Min, Virginia Polytechnic Institute and State University

Adam Morrison, Tel Aviv University

Gilles Muller, Inria

Dushyanth Narayanan, Microsoft Research

David Nellans, NVIDIA

Ed Nightingale, Microsoft Research

Sam H. Noh, UNIST (Ulsan National Institute of Science and Technology)

Aurojit Panda, New York University Peter Pietzuch, Imperial College London

Don Porter, The University of North Carolina at Chapel Hill

Michael Reiter, *The University of North Carolina* at Chapel Hill

Scott Rixner, *Rice University* Timothy Roscoe, *ETH Zurich*

Chris Rossbach, The University of Texas at Austin and VMware Research

Leonid Ryzhyk, VMware Research Bianca Schroeder, University of Toronto Liuba Shrira, Brandeis University

Keith A. Smith, *NetApp* Patrick Stuedi, *IBM Research*

Michael Stumm, *University of Toronto* Ryan Stutsman, *University of Utah*

Steve Swanson, *University of California*, San Diego Michael Swift, *University of Wisconsin–Madison*

Nisha Talagala, *Pyxeda AI* Theodore Ts'o, *Google*

Chia-Che Tsai, Texas A&M University

Joseph Tucek, *Amazon* Haris Volos, *Google*

Marko Vukolic, IBM Research Zurich

Carl Waldspurger, Carl Waldspurger Consulting

Ric Wheeler, Facebook

Dan Williams, IBM T.J. Watson Research Center Youjip Won, Korea Advance Institute of Science and

Technology (KAIST)

${\it Gala\ Yadgar}, {\it Technion-Israel\ Institute\ of\ Technology}$

Yuval Yarom, University of Adelaide and Data61

Erez Zadok, Stony Brook University Zheng Zhang, Rutgers University

#### **Extended Review Committee**

Irina Calciu, VMWare Research Group Orr Dunkelman, University of Haifa

Ittay Eyal, Technion—Israel Institute of Technology

David Grove, *IBM Research* Ajay Gulati, *ZeroStack* Tim Harris, *Amazon UK*

Gernot Heiser, University of New South Wales

Asim Kadav, *NEC Labs* Julia Lawall, *Inria/LIP6* Kfir Lev-Ari, *Apple*  Carlos Maltzahn, University of California, Santa Cruz

Jason Nieh, Columbia University

Erik Riedel, EMC

Mark Silberstein, Technion—Israel Institute of Technology

Animesh Trivedi, Vrije Universiteit Amsterdam

Ymir Vigfusson, Emerson University

Lluis Vilanova, Technion—Israel Institute of Technology

Yang Wang, Ohio State University Michael Wei, VMWare Research Group Keith Winstein, Stanford University

Guoqing (Harry) Xu, University of California, Los Angeles

Noa Zilberman, University of Cambridge

#### **Best of the Rest Session Co-Chairs**

Amy Tai, VMware Research

Chia-Che Tsai, Texas A&M University

#### **Lightning Talks Co-Chairs**

Deniz Altinbuken, Google

Aasheesh Kolli, The Pennsylvania State University and VMware Research

#### **Submissions Co-Chairs**

Lalith Suresh, *VMware Research* Gerd Zellweger, *VMware Research*

#### **External Reviewers**

Amir Gholaminejad Ben Pfaff Divyakant Agrawal Mohammad Alizadeh Adrien Ghosn Mia Primorac Jia-Ju Bai James Gleeson Amna Shahab Hitesh Ballani William Hatch Philip Shilane Dongkun Shin Tom Barbette Shachar Itzhaky Kirill Bogdanov Anand Iyer Alex Shraer Mihai Budiu David M. Johnson Igor Smolyar Aaron Carroll Rob Johnson Weijia Song Robert Soule Mosharaf Chowdhury Antonis Katsarakis Israel Cidon Eric Keller Angelos Stavrou **Tudor David** Marios Kogias Swami Sundararaman

Quentin De Coninck Richard Li Amy Tai

Giovanni Di Crescenzo Shan Lu Dmitrii Ustiugov

Aleksandar Dragojevic Peter Macko Shivaram Venkataraman

Haggai EranHaohui MaiUdi WiederAnshul GandhiKetan Mayer-PatelMatei ZahariaManya GhobadiArif MerchantBowen Zhou

# USENIX ATC '19: 2019 USENIX Annual Technical Conference

# July 10–12, 2019 Renton, WA, USA

| Refreshing ATC - USENIX ATC 19 Program Co-Chairs Message                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real-World, Deployed Systems  The Design and Operation of CloudLab                                                                                                                                                                                                                                      |

| Everyone Loves File: File Storage Service (FSS) in Oracle Cloud Infrastructure                                                                                                                                                                                                                          |

| Zanzibar: Google's Consistent, Global Authorization System                                                                                                                                                                                                                                              |

| IASO: A Fail-Slow Detection and Mitigation Framework for Distributed Storage Services                                                                                                                                                                                                                   |

| Runtimes                                                                                                                                                                                                                                                                                                |

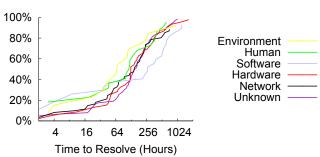

| PARTISAN: Scaling the Distributed Actor Runtime                                                                                                                                                                                                                                                         |

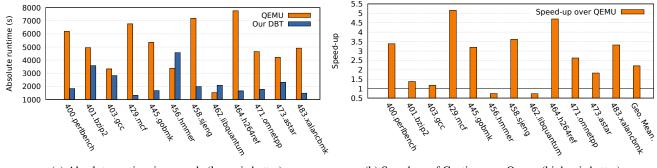

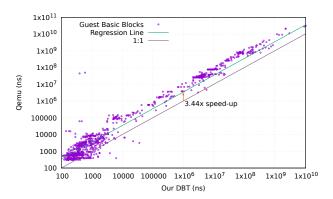

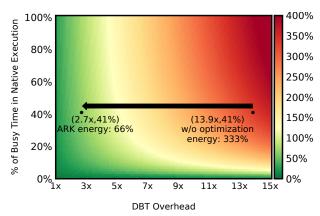

| Unleashing the Power of Learning: An Enhanced Learning-Based Approach for Dynamic Binary Translation                                                                                                                                                                                                    |

| Transactuations: Where Transactions Meet the Physical World                                                                                                                                                                                                                                             |

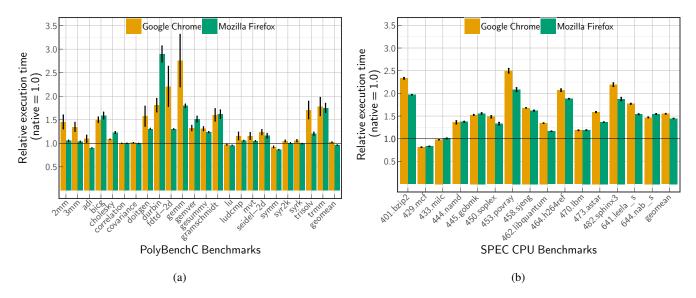

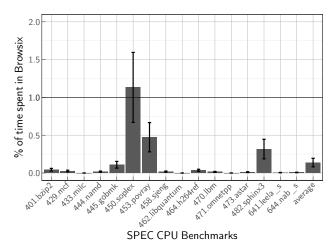

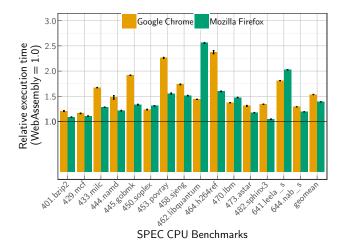

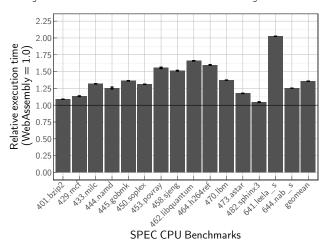

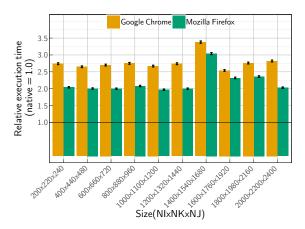

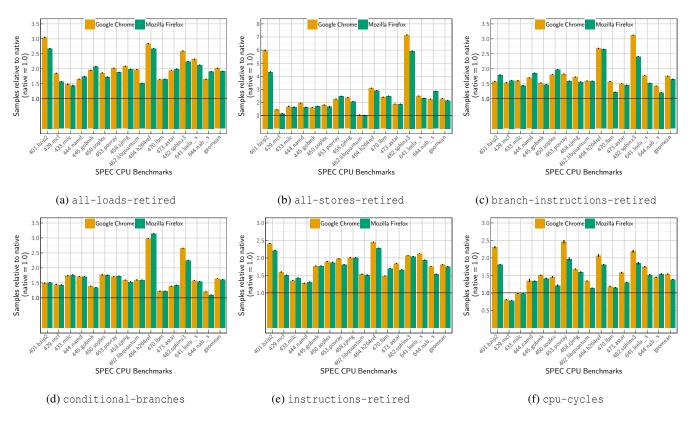

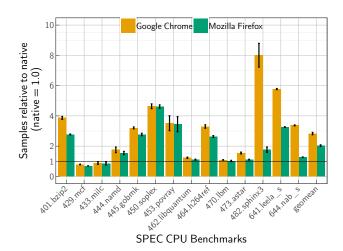

| Not So Fast: Analyzing the Performance of WebAssembly vs. Native Code                                                                                                                                                                                                                                   |

| Filesystems                                                                                                                                                                                                                                                                                             |

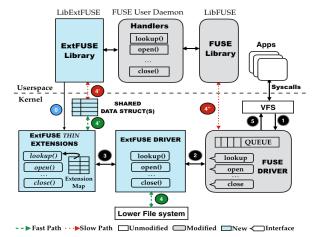

| Extension Framework for File Systems in User space                                                                                                                                                                                                                                                      |

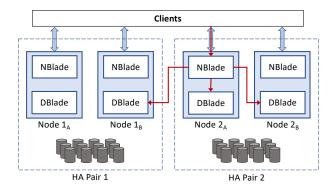

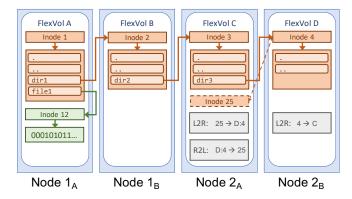

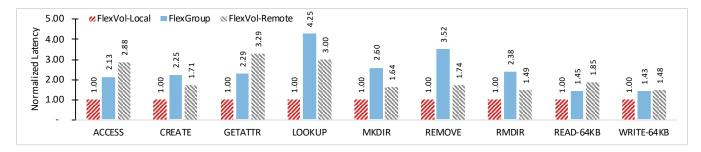

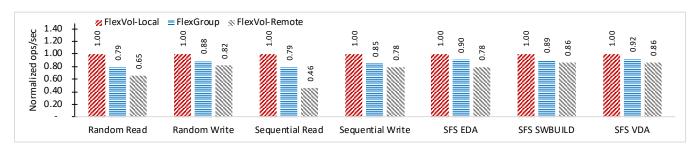

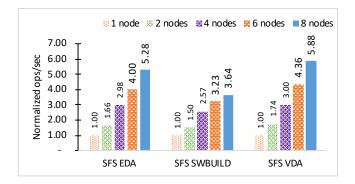

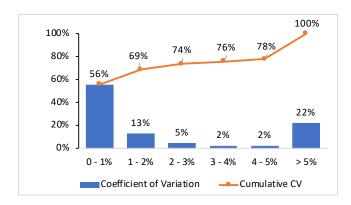

| FlexGroup Volumes: A Distributed WAFL File System                                                                                                                                                                                                                                                       |

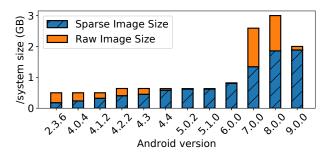

| EROFS: A Compression-friendly Readonly File System for Resource-scarce Devices                                                                                                                                                                                                                          |

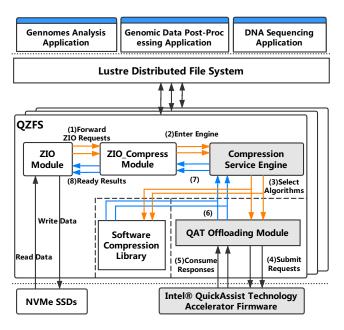

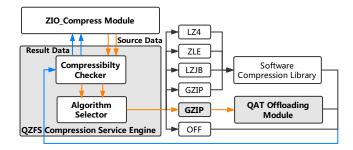

| QZFS: QAT Accelerated Compression in File System for Application Agnostic and Cost Efficient Data Storage 163 Xiaokang Hu and Fuzong Wang, Shanghai Jiao Tong University, Intel Asia-Pacific R&D Ltd.; Weigang Li, Intel Asia-Pacific R&D Ltd.; Jian Li and Haibing Guan, Shanghai Jiao Tong University |

| Big-Data Programming Models & Frameworks                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

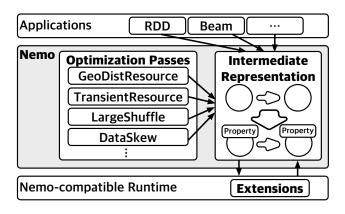

| Apache Nemo: A Framework for Building Distributed Dataflow Optimization Policies                                                                                                                                                            |

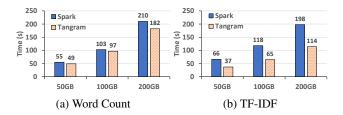

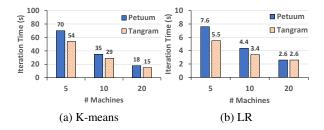

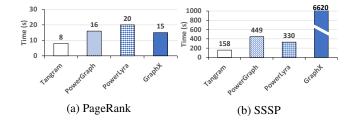

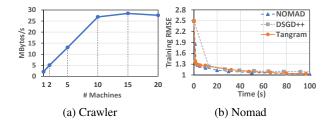

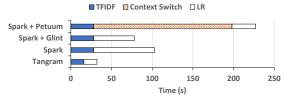

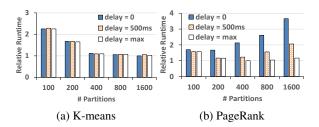

| <b>Tangram: Bridging Immutable and Mutable Abstractions for Distributed Data Analytics191</b> Yuzhen Huang, Xiao Yan, Guanxian Jiang, Tatiana Jin, James Cheng, An Xu, Zhanhao Liu, and Shuo Tu, <i>The Chinese University of Hong Kong</i> |

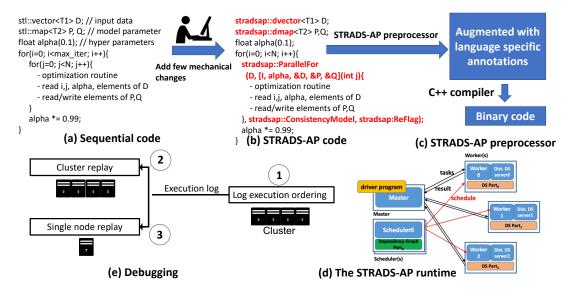

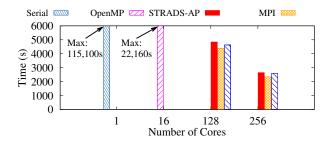

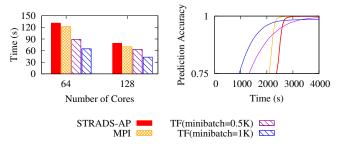

| STRADS-AP: Simplifying Distributed Machine Learning Programming without Introducing a New                                                                                                                                                   |

| Programming Model                                                                                                                                                                                                                           |

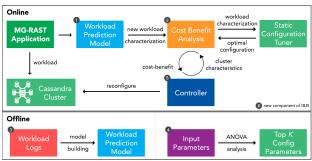

| SOPHIA: Online Reconfiguration of Clustered NoSQL Databases for Time-Varying Workloads                                                                                                                                                      |

| Security #1: Kernel                                                                                                                                                                                                                         |

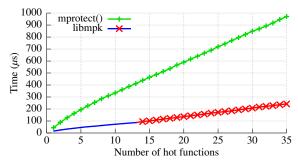

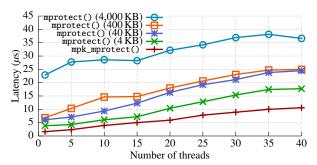

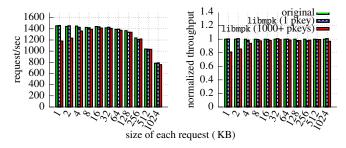

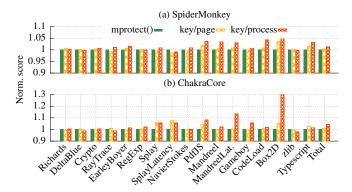

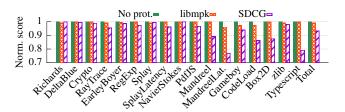

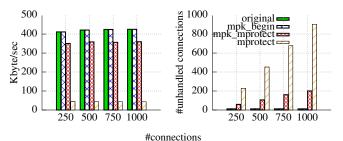

| libmpk: Software Abstraction for Intel Memory Protection Keys (Intel MPK)                                                                                                                                                                   |

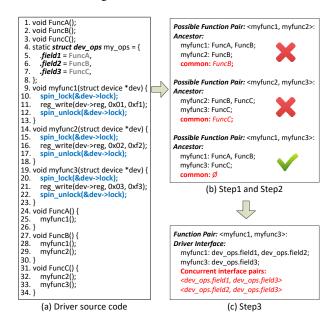

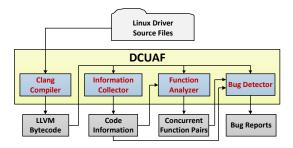

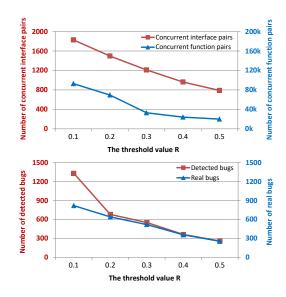

| Effective Static Analysis of Concurrency Use-After-Free Bugs in Linux Device Drivers                                                                                                                                                        |

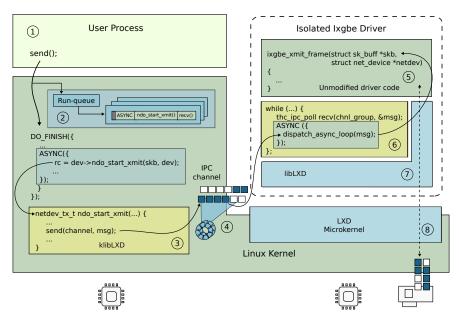

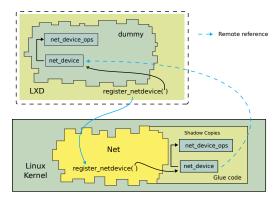

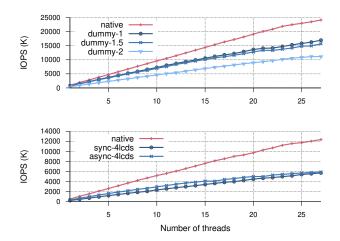

| LXDs: Towards Isolation of Kernel Subsystems                                                                                                                                                                                                |

| JumpSwitches: Restoring the Performance of Indirect Branches In the Era of Spectre                                                                                                                                                          |

| Parallelism & Synchronization                                                                                                                                                                                                               |

| Multi-Queue Fair Queuing                                                                                                                                                                                                                    |

| BRAVO—Biased Locking for Reader-Writer Locks                                                                                                                                                                                                |

| Mitigating Asymmetric Read and Write Costs in Cuckoo Hashing for Storage Systems                                                                                                                                                            |

| Programmable I/O Devices                                                                                                                                                                                                                    |

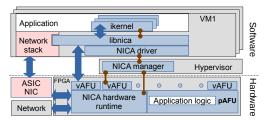

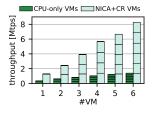

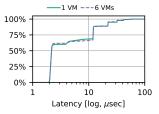

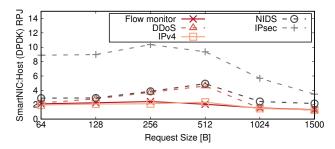

| NICA: An Infrastructure for Inline Acceleration of Network Applications                                                                                                                                                                     |

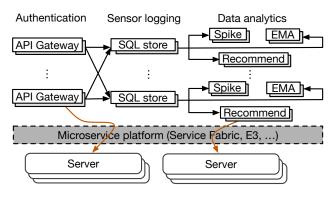

| E3: Energy-Efficient Microservices on SmartNIC-Accelerated Servers                                                                                                                                                                          |

| INSIDER: Designing In-Storage Computing System for Emerging High-Performance Drive                                                                                                                                                          |

| Cognitive SSD: A Deep Learning Engine for In-Storage Data Retrieval                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Graph Processing Frameworks                                                                                                                                                                                                                                                                  |

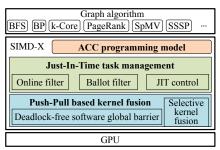

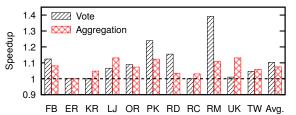

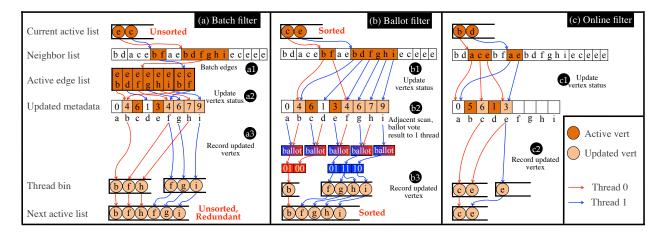

| SIMD-X: Programming and Processing of Graph Algorithms on GPUs                                                                                                                                                                                                                               |

| LUMOS: Dependency-Driven Disk-based Graph Processing                                                                                                                                                                                                                                         |

| NeuGraph: Parallel Deep Neural Network Computation on Large Graphs                                                                                                                                                                                                                           |

| Pre-Select Static Caching and Neighborhood Ordering for BFS-like Algorithms on Disk-based Graph Engines 459 Eunjae Lee, <i>UNIST</i> ; Junghyun Kim, <i>TmaxOS</i> ; Keunhak Lim, <i>Nexon</i> ; Sam H. Noh, <i>UNIST</i> ; Jiwon Seo, <i>Hanyang University</i>                             |

| Virtualization Flavors                                                                                                                                                                                                                                                                       |

| From Laptop to Lambda: Outsourcing Everyday Jobs to Thousands of Transient Functional Containers475 Sadjad Fouladi, Francisco Romero, Dan Iter, and Qian Li, Stanford University; Shuvo Chatterjee, unaffiliated; Christos Kozyrakis, Matei Zaharia, and Keith Winstein, Stanford University |

| Hodor: Intra-Process Isolation for High-Throughput Data Plane Libraries                                                                                                                                                                                                                      |

| A Retargetable System-Level DBT Hypervisor                                                                                                                                                                                                                                                   |

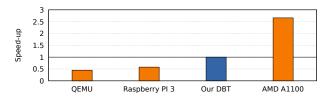

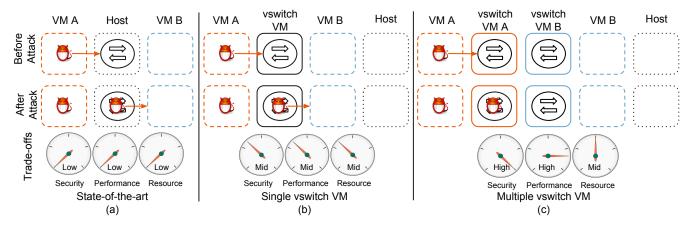

| MTS: Bringing Multi-Tenancy to Virtual Networking                                                                                                                                                                                                                                            |

| Security #2: Isolation                                                                                                                                                                                                                                                                       |

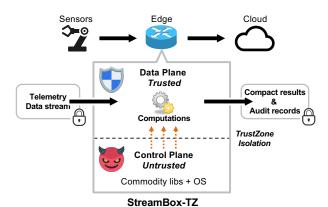

| StreamBox-TZ: Secure Stream Analytics at the Edge with TrustZone                                                                                                                                                                                                                             |

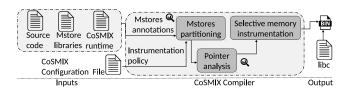

| CoSMIX: A Compiler-based System for Secure Memory Instrumentation and Execution in Enclaves                                                                                                                                                                                                  |

| Secured Routines: Language-based Construction of Trusted Execution Environments                                                                                                                                                                                                              |

| Supporting Security Sensitive Tenants in a Bare-Metal Cloud                                                                                                                                                                                                                                  |

| Exotic Kernel Features                                                                                                                                                                                                                                                                       |

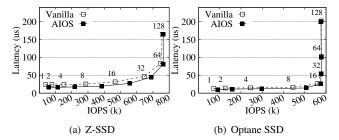

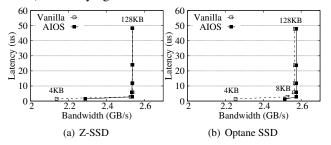

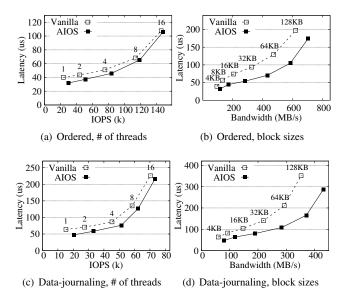

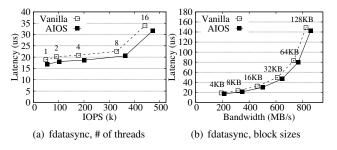

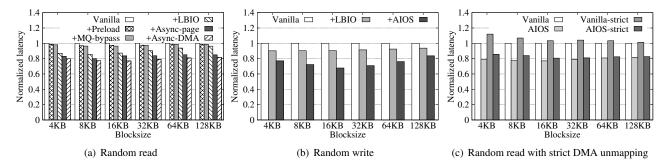

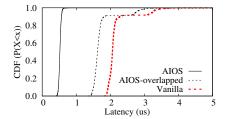

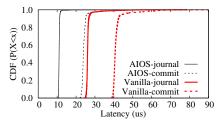

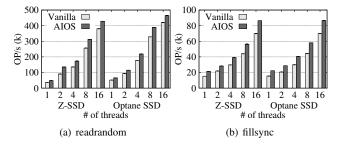

| Asynchronous I/O Stack: A Low-latency Kernel I/O Stack for Ultra-Low Latency SSDs                                                                                                                                                                                                            |

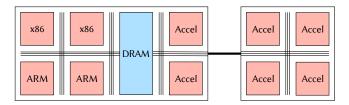

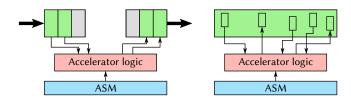

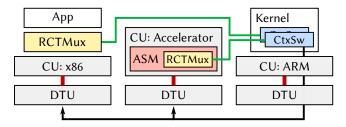

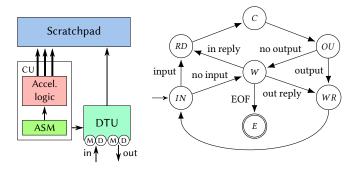

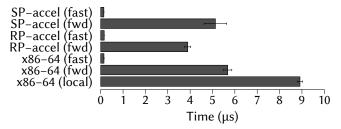

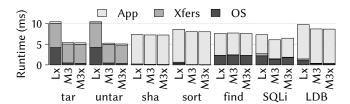

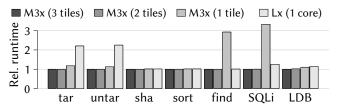

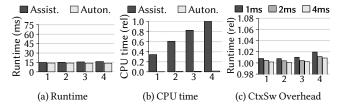

| M <sup>3</sup> x: Autonomous Accelerators via Context-Enabled Fast-Path Communication                                                                                                                                                                                                        |

| Deduplication                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------|

| SmartDedup: Optimizing Deduplication for Resource-constrained Devices                                                          |

| Data Domain Cloud Tier: Backup here, backup there, deduplicated everywhere!                                                    |

| Exotic Kernel Features #2                                                                                                      |

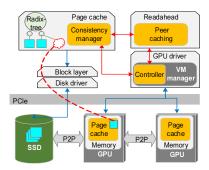

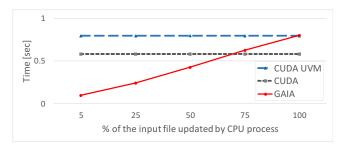

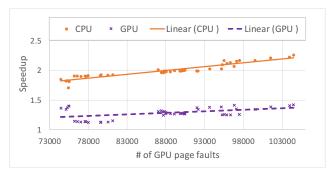

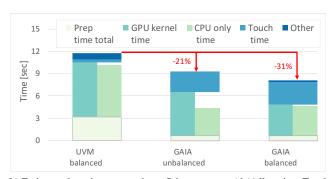

| GAIA: An OS Page Cache for Heterogeneous Systems                                                                               |

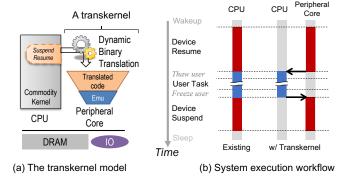

| Transkernel: Bridging Monolithic Kernels to Peripheral Cores                                                                   |

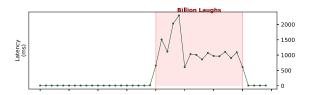

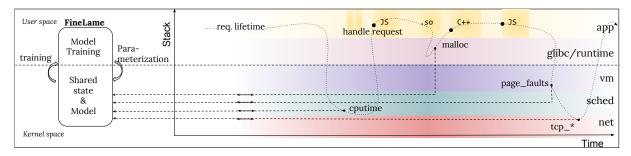

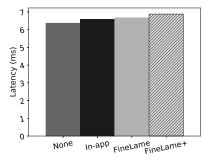

| Detecting Asymmetric Application-layer Denial-of-Service Attacks In-Flight with FINELAME                                       |

| SemperOS: A Distributed Capability System                                                                                      |

| Key-Value Stores                                                                                                               |

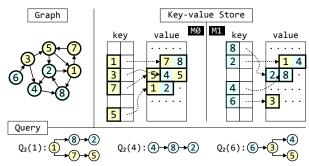

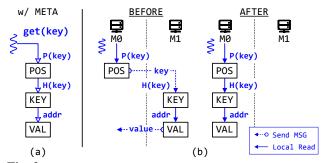

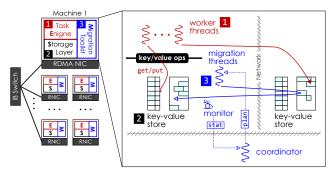

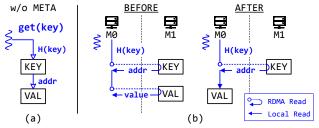

| Pragh: Locality-preserving Graph Traversal with Split Live Migration                                                           |

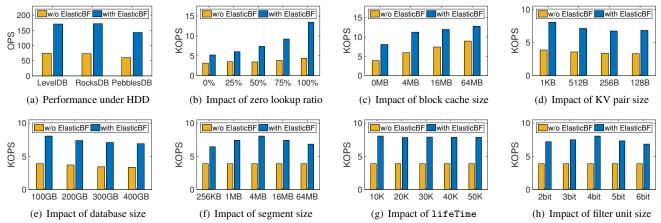

| ElasticBF: Elastic Bloom Filter with Hotness Awareness for Boosting Read Performance in Large                                  |

| Key-Value Stores739Yongkun Li, Chengjin Tian, Fan Guo, Cheng Li, and Yinlong Xu, University of Science and Technology of China |

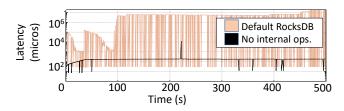

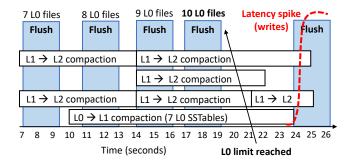

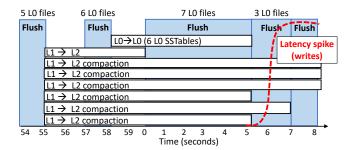

| SILK: Preventing Latency Spikes in Log-Structured Merge Key-Value Stores                                                       |

| Unification of Temporary Storage in the NodeKernel Architecture                                                                |

| Solid-State & Hard Disk Drives                                                                                                 |

| Evaluating File System Reliability on Solid State Drives                                                                       |

| Alleviating Garbage Collection Interference Through Spatial Separation in All Flash Arrays                                     |

| Practical Erase Suspension for Modern Low-latency SSDs                                                                         |

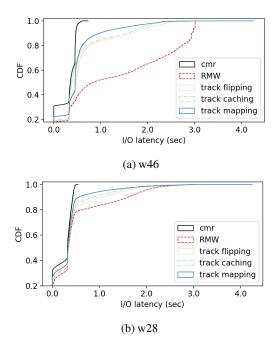

| Track-based Translation Layers for Interlaced Magnetic Recording                                                               |

| Networking                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

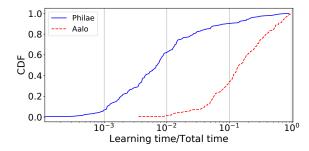

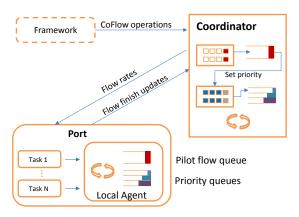

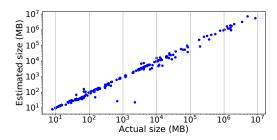

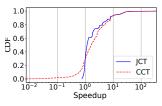

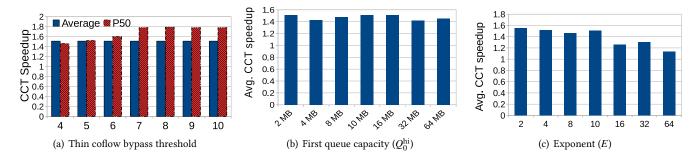

| Your Coflow has Many Flows: Sampling them for Fun and Speed                                                                                                                                                                                                                                                |

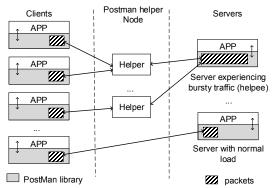

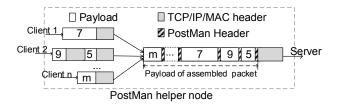

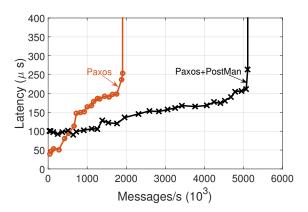

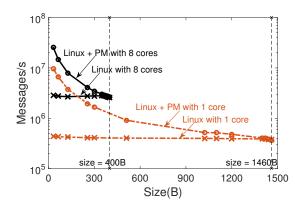

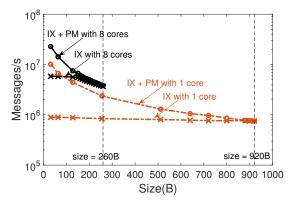

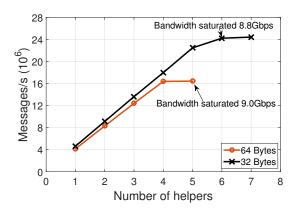

| PostMan: Rapidly Mitigating Bursty Traffic by Offloading Packet Processing                                                                                                                                                                                                                                 |

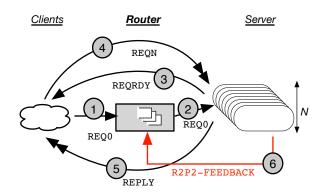

| R2P2: Making RPCs first-class datacenter citizens                                                                                                                                                                                                                                                          |

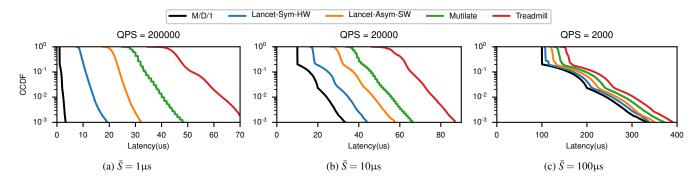

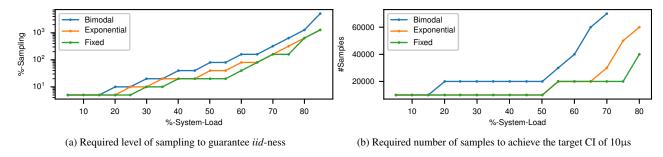

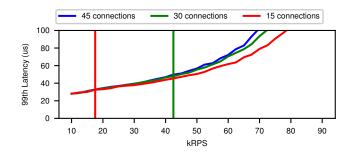

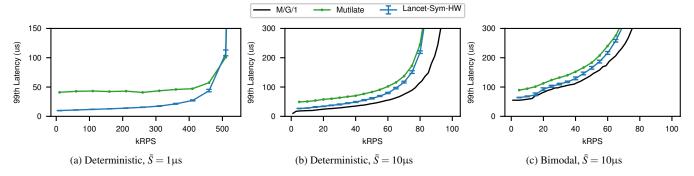

| Lancet: A self-correcting Latency Measuring Tool                                                                                                                                                                                                                                                           |

| Non-Volatile Memory                                                                                                                                                                                                                                                                                        |

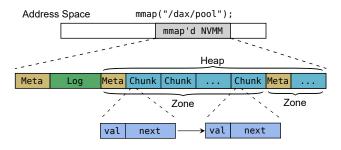

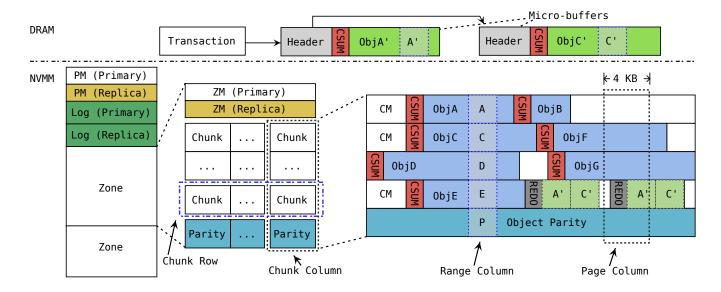

| Pangolin: A Fault-Tolerant Persistent Memory Programming Library                                                                                                                                                                                                                                           |

| Pisces: A Scalable and Efficient Persistent Transactional Memory                                                                                                                                                                                                                                           |

| Scheduling Things                                                                                                                                                                                                                                                                                          |

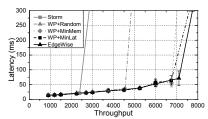

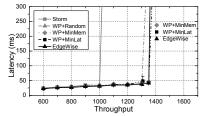

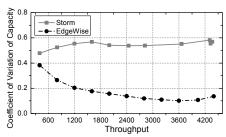

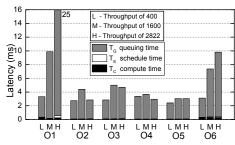

| EDGEWISE: A Better Stream Processing Engine for the Edge                                                                                                                                                                                                                                                   |

| Analysis of Large-Scale Multi-Tenant GPU Clusters for DNN Training Workloads                                                                                                                                                                                                                               |

| Storage Failure & Recovery                                                                                                                                                                                                                                                                                 |

| Lessons and Actions: What We Learned from 10K SSD-Related Storage System Failures                                                                                                                                                                                                                          |

| Who's Afraid of Uncorrectable Bit Errors? Online Recovery of Flash Errors with Distributed Redundancy977 Amy Tai, Princeton University and VMware Research; Andrew Kryczka and Shobhit O. Kanaujia, Facebook; Kyle Jamieson and Michael J. Freedman, Princeton University; Asaf Cidon, Columbia University |

| Dayu: Fast and Low-interference Data Recovery in Very-large Storage Systems                                                                                                                                                                                                                                |

| OPTR: Order-Preserving Translation and Recovery Design for SSDs with a Standard Block Device Interface 1009 Yun-Sheng Chang and Ren-Shuo Liu, <i>National Tsing Hua University</i>                                                                                                                         |

| Machine Learning Applications & System Aspects                                                                                                                                                                                                                                                             |

| Optimizing CNN Model Inference on CPUs                                                                                                                                                                                                                                                                     |

| Accelerating Rule-matching Systems with Learned Rankers                                                                                                                                                                                                                                                    |

(continued on next page)

| MArk: Exploiting Cloud Services for Cost-Effective, SLO-Aware Machine Learning Inference Serving1049 Chengliang Zhang, Minchen Yu, and Wei Wang, Hong Kong University of Science and Technology; Feng Yan, University of Nevada, Reno |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

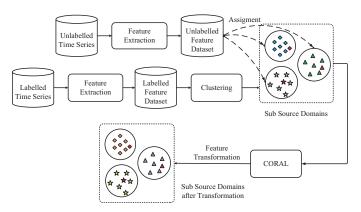

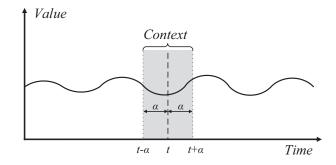

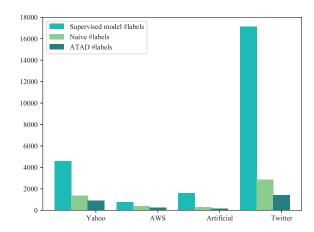

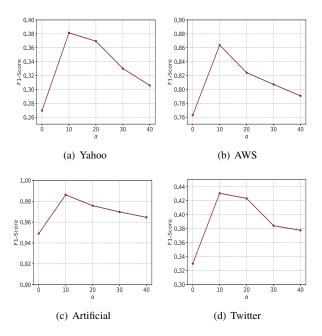

| Cross-dataset Time Series Anomaly Detection for Cloud Systems                                                                                                                                                                         |

| Xu Zhang, Microsoft Research, Nanjing University; Qingwei Lin, Yong Xu, and Si Qin, Microsoft Research; Hongyu                                                                                                                        |

| Zhang, The University of Newcastle; Bo Qiao, Microsoft Research; Yingnong Dang, Xinsheng Yang, Qian Cheng, Murali                                                                                                                     |

| Chintalapati, Youjiang Wu, and Ken Hsieh, Microsoft; Kaixin Sui, Xin Meng, Yaohai Xu, and Wenchi Zhang, Microsoft                                                                                                                     |

| Research; Furao Shen, Nanjing University; Dongmei Zhang, Microsoft Research                                                                                                                                                           |

|                                                                                                                                                                                                                                       |

## Refreshing ATC – USENIX ATC '19 Program Co-Chairs Message

## Dan Tsafrir Technion – Israel Institute of Technology and VMware Research

## Dahlia Malkhi VMware Research and Calibra

#### Introduction

Welcome to ATC '19: the 2019 USENIX Annual Technical Conference. The scope of ATC covers all practical aspects related to systems software, and its goal is to improve and further the knowledge of computing systems of all scales, from small embedded mobile devices to large data centers, while emphasizing implementations and experimental results.

The ATC '19 program is the result of tremendous efforts by many in our community. We are most thankful to the authors who submitted their high-quality work and to the reviewers who undertook the challenging task of evaluating hundreds of submissions and providing constructive feedback to the authors. While working on creating the program, we have been repeatedly inspired by our reviewers' competence, experience, patience, and dedication. Thanks to their efforts, we are happy to report that the excellent program of ATC '19 achieves its aforementioned goal.

Briefly, we received 356 submissions and accepted 71 (19.9% acceptance rate) through a double-blind, two-rounds review process. The statistics that describe the submitted and accepted papers, along with the details of the review process, are summarized in Table 1 and are further discussed below.

This document is somewhat longer than is typical for a "message from the ATC program co-chairs". What motivated us to write this detailed report is the many changes that have been introduced to ATC this year, the reasoning underlying them, and the new things we have learned while working on creating the program. The potential target audience for this document is future chairs, or readers who wish to learn more about the process.

#### Changes

We have introduced some notable changes to ATC this year, primarily to meet higher reviewing standards used by other major systems conferences. We discuss these changes next.

#### **Increased Number of Reviews**

Top-tier system conferences typically employ a two-rounds reviewing process in which each submission receives at least three reviews in the first review round (R1), and then, if the

#### description count

i. all submissions (short & full):

- submitted (458 registered) 356

- violated format, given 24 hour to fix 29

- 2 rejected+withdrawn due to said format violations

- 2 withdrawn before review process ended

- 352 underwent the full review process

- 184 promoted to review round #2 (R2)

- 80 R2 submissions pre-rejected during online discussions

- 37 R2 submissions pre-accepted during online discussions

- R2 submissions discussed at PC meeting (accepted 34)

- 71 accepted (19.9% acceptance ratio)

#### ii. short submissions:

- 32 submitted

- rejected+withdrawn due to format violations

- promoted to R2

- R2 submissions pre-rejected during online discussions

- discussed at the meeting and accepted

- full submission accepted as short

#### iii. committee & reviewing load:

- heavy weight PC members; 18-19 reviews per member

- 28 light weight PC members; 13 reviews per member

- 22 external review committee (ERC) members; 5 reviews

- 116 committee members

- 51 external reviewers; 1 review

#### iv. reviews:

- 3-4 per submission in R1 (at least 2 by heavy members)

- 5-6 per submission in R2 (at least 4 by heavy members)

- 1.347 reviews in R1

- 405 reviews in R2

- total, consisting of 1,097,815 words (6.7MB) 1,752

#### v. authors:

- 1.695 all submissions (1,442 unique, with 409 affiliations)

- 384 accepted (361 unique, with 118 affiliations)

Table 1: ATC '19 submissions and reviewing statistics.

submission is promoted to the second round (R2) based on its R1 reviews, it gets at least two additional reviews, amounting to at least five reviews per R2 submission.

In contrast, until this year, ATC R1 and R2 submissions received only two and four reviews, respectively. Upon investigation, we have learned that the decision to employ fewer reviews than other systems conferences has been made more

than a decade ago, by the program co-chairs of ATC 2008.

We and many others believe that making review-round promotion decisions based on only two R1 reviews is less informed, and hence leads to higher variability in the result. We further feel that the minimal number of R2 reviews should be similar to that of the other main system conferences, to allow for a better, more rigorous paper selection process. Consequently, this year, all submissions have indeed received at least three R1 reviews and at least five R2 reviews.

#### 2.2 Double Blindness

Ever since ATC has been established, and until this year, the conference has employed a single-blind reviewing process, whereby reviewers see the names of the authors of the submissions that they review. While simplifying the review process, studies show that single-blindness might lead to bias against minorities and in favor of well-known authors and organizations. For example, Tomkins et al. show that

"Reviewers in the single-blind condition typically bid for 22% fewer papers and preferentially bid for papers from top universities and companies. Once papers are allocated to reviewers, single-blind reviewers are significantly more likely than their double-blind counterparts to recommend for acceptance papers from famous authors, top universities, and top companies. The estimated odds multipliers are tangible, at 1.63, 1.58, and 2.10, respectively." [14]

Similarly, Goues et al. show that

"Reviewers with author information were 1.76x more likely to recommend acceptance of papers from famous authors, and 1.67x more likely to recommend acceptance of papers from top institutions. [...] When reviewers knew author identities, review scores for papers with male-first authors were 19% higher, and for papers with female-first authors 4% lower." [4]

The latter study also shows that reviewers are usually unable to deanonymize authors of submissions by guessing, even if they believe themselves to be experts on a submission's topic.

Accordingly, major systems conferences (including SOSP, OSDI, ASPLOS, Eurosys, FAST, NSDI, and USENIX Security) employ a double-blind reviewing process by keeping author identities concealed from reviewers.

For ATC '19, we employed this policy as well, and we hope future chairs will continue to do so. The ATC '19 call for papers (CFP) requires authors to make a good faith attempt to anonymize their submissions by avoiding identifying themselves or their institution, either explicitly or by implication, e.g., through references, acknowledgments, online repositories that are part of the submission, or direct interaction with

committee members. When authors cite their own studies, the CFP specifies two possibilities: either cite them as written by a third party (preferable), or as anonymized supplemental material uploaded to the HotCRP submission management system (most useful when the cited work is currently under review or awaiting publication). Prior publication as a technical report or in an online repository does not constitute a violation of anonymity.

#### 2.3 Author Responses

Most premier systems conferences – e.g., OSDI, SOSP, ASPLOS, USENIX Security – give authors a few days to write a response to the reviews. The authors' response is known as "rebuttal", and it is optional. It allows authors to provide answers to specific questions raised by reviewers and, importantly, to correct factual errors or misunderstanding in the reviews. (It may *not* provide new results or reformulate the presentation.) Some researchers perceive rebuttals as essential for the reviewing process, to keep it fair and transparent [6], and some ACM SIGs encourage program chairs and steering committees of SIG-sponsored events to employ rebuttals, based on feedback from their members [13].

Therefore, for ATC '19, we chose to allow authors to rebut. Similarly to our past experiences in forming programs while serving in committees of conferences that employ rebuttals, our sense is that the author responses have contributed to the ATC '19 process. Primarily because they allowed the reviewers to make better informed decisions in certain cases. But also because they implicitly encouraged reviewers to write more accountable reviews and, importantly, to submit them on time so as to be visible during the authors response period; the latter allowed the online discussion period to start on time with all the required material available.

We used a 500-words soft limit on the size of the rebuttal; reviewers were not required to read more. The reviews were made visible to authors in the rebuttal period, during which reviewers were asked to avoid modifying them. After the rebuttal period ended, reviews became invisible to authors again, allowing reviewers to update them based on the rebuttal, the online discussions, and the program committee (PC) meeting.

#### 2.4 Submission Chairs

The ever-increasing number of submissions to systems conferences (approaching 400 in the last two ATCs) makes it increasingly challenging for everyone involved to create a program. For example, it is challenging for reviewers to bid on hundreds of submissions so as to express review preferences. It is likewise challenging to arrange things such that the submission system accurately reflects conflicts associated with more than a hundred reviewers and an order of magnitude more authors (experience repeatedly shows that many conflicts are missing because reviewers and authors neglect

to declare all their conflicts). It is also challenging to manage a "dual track" PC meeting (where the PC is split between two rooms part of the time) in a manner that ensures that all committee members are found in the right room at the right time in order to discuss the submissions they have reviewed. Many other examples exist.

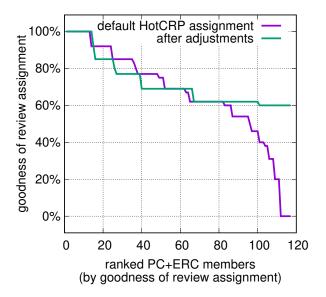

For this reason, we decided to formalize the role of a "submission chair" as part of the official organizers of ATC. The job of the submission chair is to help the program chair in accomplishing tasks such as those listed above by, for example: adding missing conflicts to HotCRP based on DBLP; helping reviewers' bidding by identifying the submissions that cite their papers and communicating this information to the reviewers; checking format violation in uploaded PDFs and communicating with authors to quickly fix those through reformatting and content deletion; helping to ensure that the quality of the reviews assignment is high (HotCRP assignments might be far from optimal); helping to make sure that per-submission administrative tasks are being carried out and progress is achieved, e.g., by following up on submissions that were not yet tagged as passing the "review sufficiency check"; helping in scheduling of the dual track meeting; and serving as scribes during the meeting while making sure the scheduling of PC members in rooms works as expected.

Submission chairs get admin privileges in the HotCRP system in order to carry out their duties. Their role, however, never requires them to make decisions that affect the outcome of the review process. For example, they do not steer online discussions. It is productive for the program chair and submission chair to be geographically located near each other, allowing them to physically meet when the need arises.

#### 2.5 **Extended Review Committee (ERC)**

Most of the premier systems conferences, which must review a few hundreds of submissions, typically employ a light-heavy program committee model, where "light" PC members review fewer submissions but do not attend the PC meeting, whereas "heavy" members review more submissions and attend the meeting. This model is needed in order to decrease the high reviewing load of PC members, while keeping in mind that the number of people who can sit in one room and conduct a productive discussion is bounded.

Last year, unpredictably, ATC '18 received nearly a hundred additional submissions as compared to ATC '17 (377 submissions as compared to 283 submissions, respectively). To our knowledge, the PC of 2018 was the the first ATC PC to employ the light-heavy model. In previous years, all ATC PC members were "heavy", which was viable because the number of submissions was much lower, albeit, even so, past ATC-s reviewing load was sometimes in the range of 25–30 submissions per member. (Some of us were members of those PCs and still remember the pain.)

Our goal for this year was to ensure that the reviewing load

of heavy members will not exceed 20 submissions. In parallel, USENIX instructed us to be prepared for an additional sizable increase in the number of submissions. Therefore, to be safe and have some flexibility, we decided to supplement the lightheavy model with an Extended Review Committee (ERC), consisting of members whose review load will be light: about 5 submissions per member.

Notably, due to the light reviewing load, ERC members were easy to draft regardless of their seniority: they typically accepted our invitation (which specified that the expected reviewing load will be 3–7). Additionally, more than a quarter of the ERC members were initially invited to serve as heavy or light members and opted for the lighter alternative instead of declining altogether.

Ultimately, having an ERC was a contributing factor that allowed us to assign four reviewers in R1 to most submissions (without increasing the load on light and heavy members beyond our planned upper bound). Having an initial assignment of four reviews proved to be invaluable when making R2 promotion decisions in the face of multiple late reviews, as three reviews were typically enough to confidently make the call. The ERC members additionally contributed by augmenting the expertise of our pool of reviewers.

#### No Abstract Submission Deadline

Last year, in their welcome message, the program co-chairs of ATC '18 stated that

"We required authors to submit abstracts a week before the paper submission in the hope of ensuring proper subject area coverage by the program committee and to get an idea of the reviewing load. This did not work. We had over 550 submitted abstracts, meaning almost 40% of the submissions were abandoned. In the end, requiring abstracts to be submitted early did not help with planning due to such a large number of abstracts that did not result in a submission" [5].

To that we add that requiring committee members to indicate reviewing preferences before the submission deadline would be a waste of their valuable time, as they will inevitably bid on submissions that will not materialize. Stating review preferences given hundreds of finalized submissions is already time-consuming and challenging enough, and needlessly making this task even harder is counterproductive.

Bidding on registered abstracts that will not materialize into submissions would additionally negatively affect the quality of the review assignment, because committee members frequently stop bidding when they feel they have already placed "enough" bids on submissions.

Consequently, this year, we have to cancel the requirement to register abstracts in advance, and we eliminated the corresponding deadline.

#### 2.7 **Submission Deadline Closer to New Year**

The date at which accept/reject notifications for ATC submissions are sent to authors is typically set by USENIX to around mid April. Accordingly, since 2013, the submission deadline of ATC has been scheduled at the end of January or in early February, which thus far allowed the committee to complete the reviewing process in time to comply with a mid-April author notification date. This year, however, we set an earlier submission deadline: January 10, 2019.

Three issues necessitated this change. First, we needed additional time for the authors response period (Section 2.3) and for the "review sufficiency check" period that preceded it (described in Section 8). Second, as noted in Section 2.6, we had to allocate a few days following the deadline to allow reviewers to place bids on submissions indicating their review preferences; traditionally, such bidding took place before the submission deadline, as authors were required to register an abstract a week in advance.

The third issue that motivated an earlier deadline is the increased number of submissions. To cope with this increase, we allocated two weeks for online committee discussions scheduled before the PC meeting, in order to allow the committee to converge to a decision regarding as many submissions as possible—failing to do so would mean ending up with too many submissions to discuss at the meeting. The increased submission number also required allocating the week following the bidding period in order to assign reviews to members in a manner that would later allow us to reasonably conduct a dual track PC meeting (see details in Section 6).

Scheduling the submission deadline to occur soon after New Year may partially explain this year's somewhat smaller number of submissions as compared to last year: 377 vs. 356 in ATC '18 and ATC '19, respectively.

#### 2.8 **Uniform Shepherding**

In the past, shepherding in ATC was not used by default. This approach reduces the load from both committee members and authors. A main drawback, however, is the increased likelihood that some of the issues that the reviewers expect authors to address in the camera-ready version remain unresolved.

The alternative approach, used by most of the premier systems conferences, is to assign shepherds to all accepted papers and thereby generally improve quality assurance. As part of our efforts to update the ATC reviewing process in order to make it aligned with that of its sibling conferences, this year, we decided that all accept decisions are conditional and depend on the approval of shepherds.

After the (conditional) accept notification, authors were given a few days to consider how to address the reviewers' comments and email a revision plan to their shepherd. Authors and shepherds then agreed on a timeline that allows the authors to complete the revision, providing enough time for the shepherd to read, consider, and discuss the revision with the authors, while permitting a final round of text polishing if necessary before the camera-ready deadline. At the end of this process, shepherds explicitly "signed off" the inclusion of papers in the program using HotCRP tags, allowing the program chairs to track the progress of turning all conditional accepts to accepts.

#### Accept as Short

As members of former ATC PCs, we are aware of full submissions that were accepted to past ATC-s on the condition that their authors will reduce their size to meet the short paper page-limit requirement. ATC program committees made such decisions rarely, limiting them to situations where the alternative is to otherwise reject the paper.

Surprisingly, past ATC call-for-papers were not clear about the possibility to accept as short; the practice was only anecdotally documented in the messages from chairs [2]. Seeing that this practice has been used in the past and may be used in the future, in the interest of transparency, we decided to explicitly declare it in the CFP, which now states that "the program committee may rarely decide to accept a full submission on the condition that it is cut down to fit in the short paper page limit" [19].

This CFP update initiated a discussion with USENIX board members who were concerned that the effort required to transform a full submission to a short paper might be too significant to accomplish between the authors notification date and the camera-ready date. They cited the FAST policy—which states that "the program committee will not accept a full paper on the condition that it is cut down to fit in the short paper page limit" [20]—as potentially preferable.

After consideration, we decided to keep the ATC acceptas-short policy because we believe it produces a significantly better outcome for both the authors and for the community, provided the alternative is to reject. In such rare cases, disallowing the PC to accept as short would result in a lose-lose situation: the authors lose because they are rejected instead of being given a chance to shorten and thereby get accepted; the ATC program loses a short paper; and the systems community loses because the paper would be subsequently resubmitted and hence re-reviewed, requiring the community to spend additional reviewing cycles, whereas reviewing load is already too high.

<sup>&</sup>lt;sup>1</sup>In odd years, if the appropriate coordination takes place (as is the case this year), ATC notifications occur shortly before the SOSP submission deadline, to allow rejected authors of the former conference to submit an improved version of their study to the latter conference, assuming they have kept working on it while it was under submission at ATC.

#### **Shorter Presentations** 2.10

Last year's aforementioned 33% increase in the number of ATC submissions (377 in ATC '18 vs. 283 in ATC '17) and the consequent 27% increase in accepted papers (76 in ATC '18 vs. 60 in ATC '17) motivated the program co-chairs of ATC '18 to avoid hosting "best of the rest" sessions in their program, as well as to generate a longer-than-usual program that ends in the evening of the third day of the conference rather than around lunch time.

Despite having a similarly-sized program this year (71 papers), we wanted to have our cake and eat it too, namely: bring back the "best of the rest" sessions; further add lightning sessions to the program (see Section 2.12); while still end the program around lunch time at the third day, as was done in previous years prior to ATC '18.

To this end, this year, we decided to shorten the presentation time from 25 minutes per paper to 20 minutes. We believe that this change constitutes a reasonable compromise, allowing the conference to accommodate the additional sessions within the traditional time frame, while still providing enough time for presenters to convey the gist of their ideas.

#### **Poster Requirement** 2.11

To partially compensate for the shorter presentation time slots, this year, we dedicated the two poster sessions exclusively to accepted papers, and we required all paper-presenting authors to additionally present a poster in one of these sessions. Hopefully, this format will promote and facilitate interaction between authors and attendees who are interested in their work.

#### 2.12 Lightning Sessions

In recent years "lightning sessions" have become standard in top-tier computer architecture conferences (ISCA, ASPLOS, etc.), and this year we decided to adopt them in ATC. Lightning sessions are typically interesting and fun, and, importantly, they are particularly suitable for conferences that have parallel sessions, which inevitably means attendees miss some of the presentations they are interested in. Lightning sessions give attendees a chance to make more informed decisions regarding what interests them the most and which talks are more worthy of their time. Speakers indeed often treat their lightning session presentations as previews aimed at soliciting listeners to attend the associated talks.

A lightning session is a joint session at the beginning of the day, which includes all the talks that will be given on that particular day. After the daily lightning session, the conference splits into its parallel tracks. Shortly before the daily lightning session, the speakers of that day queue in order—they do not sit until they present. Then, each lightning talk is allocated 120 seconds.

Each daily lightning session has a session chair. The chair is responsible for: interacting with speakers to get their slides beforehand; ordering slides on her laptop based on their order in the program, and making sure they display nicely; informing the speakers regarding the order; and regulating time during the session if necessary (we have never witnessed a lightning session chair having to actually exercise this authority).

Lightning speakers are additionally requested to submit lightning videos beforehand, which are made available in the conference web page before the conference. Both lightning presentations and videos are currently available in the ATC '19 technical sessions webpage.

In the past, USENIX conference talks were videoed, a very useful service that largely stopped due to financial reasons. Our hope is that lighting videos, which do not incur video recording costs, can partially provide some of this service: optimally, lightning videos would allow people who wish to only understand the gist of the idea to do so in 120 seconds.

#### **Changes to Consider**

#### **Steering Committee**

The one remaining notable difference between ATC and its sibling academic systems conferences (USENIX-sponsored: FAST, NSDI, OSDI, USENIX Security; SIGOPS-sponsored: ASPLOS, Eurosys, SOSP) is that ATC does not have a formal, broad, long-term steering committee. To make ATC more valuable to the community, we-nearly all ATC program chairs since 2015—believe that ATC should have such a committee, and we propose to form it, thus completing the transition of ATC into a conference that is governed by policies generally acceptable in the academic systems community.

We propose that the newly formed ATC steering committee will assume all responsibilities typically assigned to such committees, including providing advice and guidance to the current program co-chairs, selecting future program co-chairs, sustaining organizational memory, suggesting and considering new ideas when the need arises; and ultimately shaping the role of ATC. The identity of the steering committee members should be publicized along with call-for-papers to allow interested parties to address the committee with respect to matters that concern the conference long-term.

The members of the committee could, for example, be the USENIX executive director, relevant members of the USENIX board, and the program chairs from the last n ATC instances, such that members who chaired ATC in year Y - n will be replaced by the ATC chairs of year Y shortly after the latter conference takes place. Joining the steering committee will of course be voluntary.

In October 9, 2018, a letter consisting of the content of this subsection has been submitted to the USENIX board. The letter was signed by all the ATC program chairs since 2015 except two (one responded too late and the other serves on

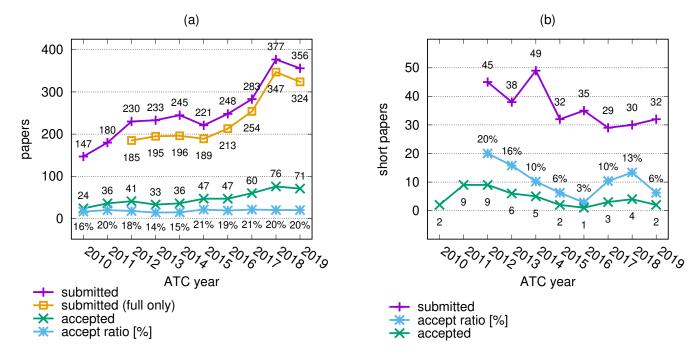

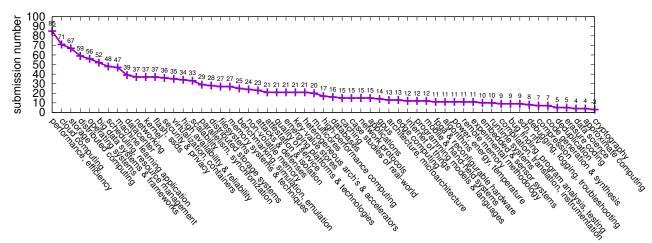

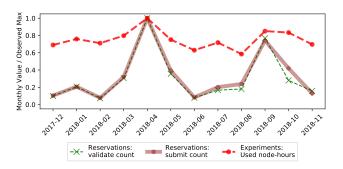

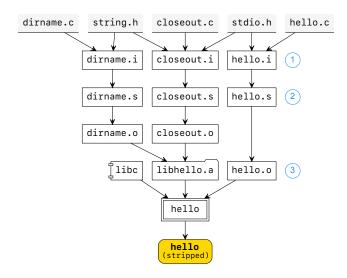

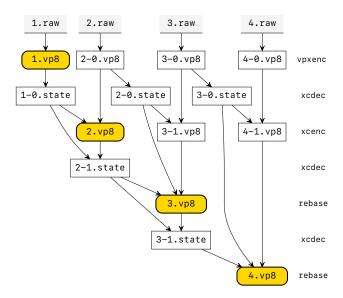

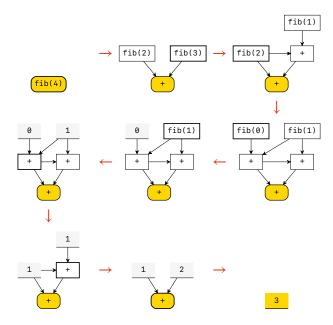

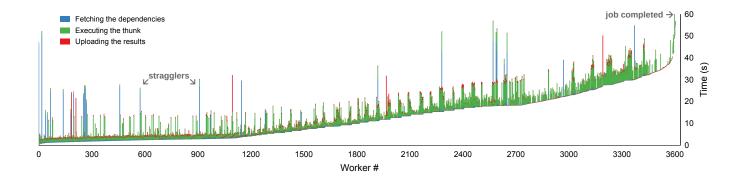

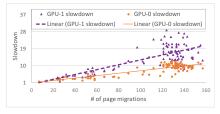

Figure 1: (a) Submission and acceptance statistics of ATC papers (including both full and short) in the last decade, based on the corresponding proceedings' message from the ATC program chairs. (b) The same, but only for short papers. In 2010–2011, short submission numbers were not reported. In 2019 and 2013, one and three of the accepted short papers were submitted as full, respectively; we do not have this information for the other years.

the Usenix board and is one of the decision makers regarding the steering committee issue). All who signed volunteered to serve on the steering committee when it is formed. The response of the relevant people in USENIX seems positive, but a steering committee has not yet been established.

#### **Test of Time Award** 3.2

All the premier systems conferences—except ATC—annually recognize historical, influential papers that have stood the test of time. This includes: USENIX Test of Time Award for FAST, NSDI, and USENIX Security [18]; SIGOPS Hall of Fame Award, which is typically handed to SOSP and OSDI papers [17]; Eurosys Test of Time Award [16]; and SIGARCH/SIGPLAN/SIGOPS ASPLOS Influential Paper Award [15].

The procedure to select the awarded papers varies. A common way employed is for the program committee of the conference to nominate influential papers published in that conference around ten years ago, with the final selection being made by the conference's steering committee (which, as noted, ATC still does not have). ATC is much older than ten years and, arguably, has changed its nature and goals over the years. So when/if an ATC test of time award is established, the steering committee will need to decide how to address older papers and handle the backlog. Jeff Mogul documented some of SIGOPS's considerations when establishing its Hall of Fame

Award in 2005 and addressing similar questions [12].

#### 3.3 **Short Submissions**

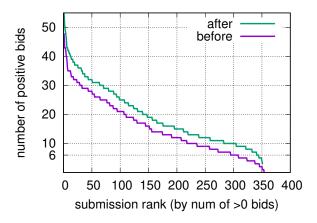

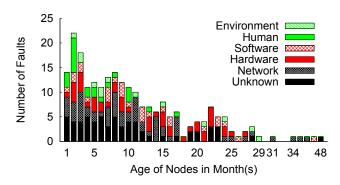

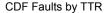

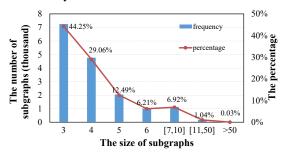

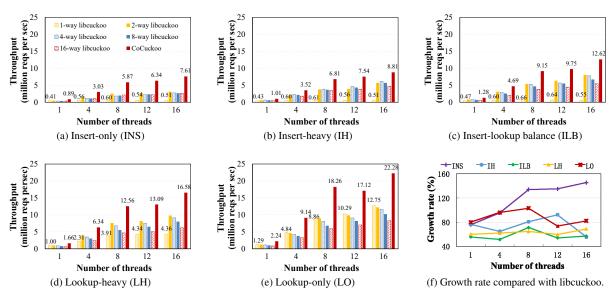

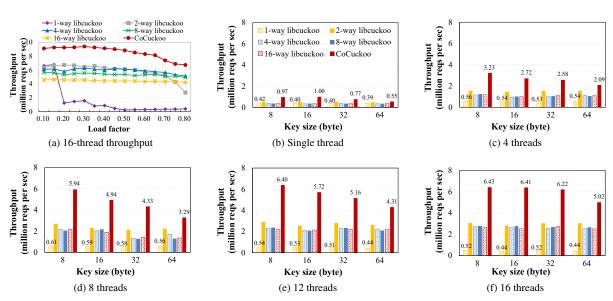

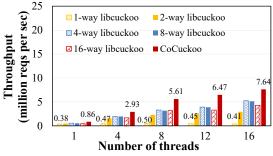

Figure 1a shows the submission and acceptance numbers of ATC papers in the last decade. Figure 1b shows the same statistics for short papers only. Getting a short submission accepted to ATC is clearly harder. We do not know why and can only speculate about the reason. Perhaps there is a mismatch between PC members' expectations and what can actually be accomplished in the scope of a short paper. Perhaps authors wrongfully believe that the bar for short submissions is lower. And perhaps there is a loose negative correlation between the increasing number of full submissions and the decreasing number of accepted short papers because PC members feel they have stronger papers to accept, relatively speaking.

Regardless of the reason, the fact that ATC PCs have reviewed 29-35 short submissions per year in the last five years only to accept 1-4 of them raises the question of whether the effort is worth it, since the reviewing effort to accept short papers is significantly greater than the effort to accept full papers (3%-13% vs. about 20% acceptance rate for short and short+full submissions in the last five years, respectively).

This year provides an extreme demonstration of how much harder the PC has to work in order to accept short papers. Table 2 specifies the number of reviews that the ATC '19 PC wrote for full and short submissions, as well as the resulting

| scenario                 | submission | written | accepted | work  |

|--------------------------|------------|---------|----------|-------|

|                          | type       | reviews | papers   | ratio |

| real (worst case)        | full       | 1620    | 70       | 23:1  |

|                          | short      | 132     | 1        | 132:1 |

| extrapolated (best case) | short      | 132     | 4        | 33:1  |

Table 2: The number of reviews that the ATC '19 PC wrote for full and short submissions demonstrates that the PC had to work much harder in order to accept a single short paper ("real"). Even if we hypothetically assume that the PC had accepted four short paper instead of one as in last year (best case scenario in the last five years), the reviews-to-accepts work ratio would still be nearly 1.5x higher ("extrapolated").

number of accepts. It turns out that the PC wrote 132 reviews in order to accept a single short paper, as opposed to writing "only" 23 reviews in order to accept a full submission. Namely, the PC had to work nearly 6x times as hard.

That said, as can be seen in Figure 1b, this year has been especially bad for short submissions. But even if we hypothetically assume the best case scenario across the last five years of accepting four short papers, the corresponding reviews-toaccepts ratio would have been 35:1, which is still nearly 1.5x harder than accepting a full paper.

ATC enjoys a steadily increasing number of full submissions. As a consequence, the reviewing load becomes heavier, requiring bigger PCs that already hardly fit into one room. Considering the relatively low return on investment (a significantly higher reviews-to-accepts ratio), it may make sense for future ATCs to consider to stop soliciting short papers.

We note in passing that, this year, we revised the CFP definition of short submissions to exclude workshop-style papers ("a short paper is not like a workshop paper—it presents a complete idea, which does not require full length to be appreciated" [19]). We introduced this change hoping to increase the short submission success rate by discouraging authors from submitting work that (our experience suggests) ATC reviewers tend to reject. The data shown in Figure 1b suggests this change was ineffective.

#### 3.4 Early Rejects or R1 Rebuttals

The program co-chairs of this year debated about the issue of whether or not to send early reject notifications to authors of submissions who did not make it to R2. The reasoning to oppose sending early rejects was that such notifications might provide an unfair advantage to R1 rejects over R2 submissions that will be rejected later on, because the authors of the former will be free to resubmit their work elsewhere much sooner. Additionally, early rejects might translate to even higher reviewing loads that the community must handle due to said earlier resubmissions. Lastly, and importantly, postponing the R1 reject notification would allow PC members to re-calibrate during the second round and the deliberations and potentially

change their opinion.

The reasoning to supported early rejects was that delaying reject notifications would be counterproductive for authors who do not abuse the system but rather leverage the reviewers' feedback to improve their work before they resubmit. Arguably, the ATC reviewing process should not replace one evil ("helping" authors who might abuse the system by ignoring the reviewers' feedback and resubmitting prematurely) with another (allowing authors to believe that they have a chance to get accepted for a good few weeks whereas in fact they do not).

Eventually, since we already introduced many changes to ATC this year (Section 2), we decided to leave things as they are in this particular case and avoid sending early reject notifications. But we encourage future ATC program chairs (and/or the ATC steering committee if it is established) to reconsider.

Because decisions were collectively sent to authors shortly after the PC meeting, R1 rejects were given a chance to write a rebuttal (Section 2.3), which the committee members read and considered. Two R1 rejected submissions were resurrected as a result. These submissions were promoted to R2 and urgently assigned two additional reviewers. In the end, however, both were rejected. We speculate that allowing authors to rebut (also) after R1 (as is done by some conferences) would have had a bigger effect. But doing so would require more labor and an even earlier deadline, which would be closer to New Year, which might result in fewer submissions (see Section 2.7).

#### **Physical PC Meeting** 3.5

The number of submissions the PC can discuss in one day (let us denote it as c) is bounded. For example, it takes more than eight hours to discuss c = 70 submissions if allocating 7 minutes per submission, as is typical. PCs also usually dedicate 2-3 minutes to present each submission that was pre-accepted in the online discussion phase (ATC '19 had 37 such submissions), and they take about 30 minutes for lunch. It is challenging to squeeze all these activities into one day.

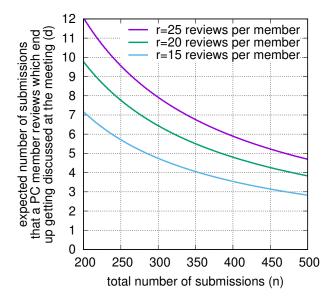

Let m denote a member of the PC, and let r denote the number of submissions reviewed by m. Similarly to c, the value of r is bounded. At the risk of overgeneralizing, we roughly approximate that r = 15, r = 20, and r = 25 reviews per member are nowadays considered light, average, and heavy reviewing loads in academic systems conferences, respectively. The value of r cannot be raised arbitrarily.

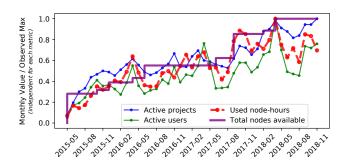

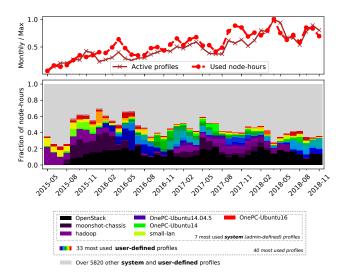

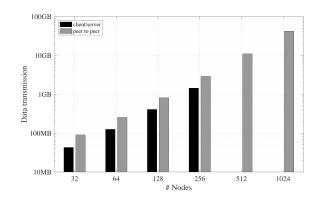

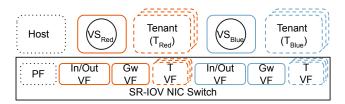

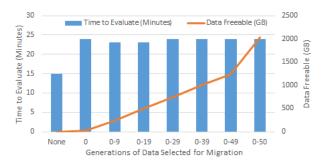

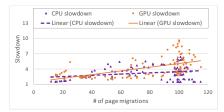

In contrast to c and r, the total number of submissions that the PC must review (let us denote it as n) is unbounded and keeps increasing. The practical meaning of this increase is that, on average, fewer and fewer of the r submissions that m reviewed are getting discussed at the meeting. Figure 2 demonstrates this trend, assuming c = 70 submissions are discussed at the meeting, and that 2/3 and 1/3 of the r submissions assigned to m are reviewed in R1 and R2, respectively. The x axis shows n, and the y axis shows the corresponding

Figure 2: Increased number of submissions translates to fewer submissions that each PC member gets to discuss at the PC meeting; see Appendix A for details.

expected number of submissions that have been reviewed by m and ended up being discussed at the meeting (let us denote it as d), which is monotonically decreasing.

In Appendix A, we show that under our assumptions,  $d \approx 4rc/3n$  is a reasonable approximation of the expected number of submissions that m reviewed and discussed at the meeting. As noted, because r and c (numerator) are bounded, d asymptotically behaves like 1/n (denominator).

Our PCs received n=356 submissions and used an upper bound of 18–19 reviews per heavy member, which more or less corresponds to the line associated with r=20 in Figure 2. In the relevant range of n, we see that d=5.5 submissions discussed at the meeting per member. Because d is just an average, some members discussed more submissions, but others discussed less: as little as 2–3 submissions in certain cases. Flying to California to discuss such a small number of submissions is, arguably, counterproductive.

In 2018, the PC meeting spanned across two days, allowing the committee to make fewer decisions during the online discussions period and instead discuss c=124 submissions in person at the meeting (with n=377 and r=18). Therefore, by our calculation, each member discussed about 8 submissions on average, alleviating the problem somewhat. On the other hand, 8 submissions during two days means 4 submissions per day (as compared to 5.5 per day in 2019), which is not necessarily preferable.

When discussing this issue with some of the members during the PC dinner, it seemed like most agreed that there is a problem: the time overhead and carbon emission associated with physical PC meetings are possibly becoming excessive considering the smaller number of submissions that each mem-

ber gets to discuss. Still, there was a sense that the program turned out better due to the physical meeting, which allowed the members to calibrate. Additionally, several members—both junior and senior—pointed out that a notable value they get from PC meetings is the chance to network and interact with their peers.

In light of the above, it may be advisable for future program chairs to consider if in-person, physical PC meetings are worth it, at least in their current format. If they decide in favor of physical meetings, one conceivable way to increase their value is, for example, to couple them with workshop-style events, where committee members briefly present their ideas and get feedback from their peers.

#### 4 Assembling the Committee

After we accepted the position of the ATC '19 program cochairs, we were asked by USENIX to take into account that the number of submissions in 2019 might exhibit the same growth rate as it did in 2018, which would bring us to about 500 submissions (a.k.a. "the nightmare scenario" :-)), requiring  $3 \times 500 + 2 \times 250 = 2000$  reviews assuming 50% of the submissions move to R2 (see Section 2.1). A smaller, more conservative estimate of 400 submissions would require  $3 \times 400 + 2 \times 200 = 1600$  reviews. In comparison, a sizable heavy PC of 60 members each contributing 20 reviews—a threshold we were hoping and planning not to exceed—provides  $60 \times 20 = 1200$  reviews. Taking into account these numbers, we decided to draft a heavy PC, a light PC, and an ERC (see Section 2.5) with target sizes of 65, 25, and 25, respectively.

Drafting about 115 committee members is a challenging task. In preparation for it, we compiled a list of all those who served on PCs in the last three instances of the main systems conferences, such that we had a pool of candidates to helps us (we used: ASPLOS 2017–2019, ATC 2016–2018, Eurosys 2017–2019, FAST 2017–2019, NSDI 2017–2019, OSDI/SOSP 2016–2018, and USENIX Security 2016–2018).

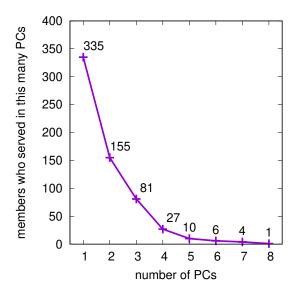

Analyzing this database brought up an interesting insight, which might indicate that our community has scalability issues in terms carrying out the reviewing load. Table 3 shows the relevant statistics. The aggregated sum of the size of the 21 PCs we have included in our analysis is 1118. These membership positions were manned by 655 unique individuals, a finding that could be interpreted to mean that members serve in  $1118/655 \approx 1.7$  PCs in three years, on average. A deeper look at the data, however, reveals that 284 individuals participated in two or more of the PCs in our database, and these individuals are responsible for manning 783 (70%) of the 1118 positions. This finding implies that a relatively small group of people shoulders most of the reviewing load.

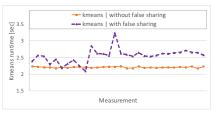

Figure 3 depicts the histogram of how many of the members in our database (y) served in how many of the PCs that we included (x), which demonstrates the reviewing effort dis-

| memberships (aggregated sum of PC sizes) | 1,118 |

|------------------------------------------|-------|

| number of unique members                 | 655   |

| number of unique recurring members       | 284   |

Table 3: Membership statistics of the PCs of the main systems conferences in the last three years.

Figure 3: Histogram showing how many of the members of the PCs of the main systems conferences in the last three years (y axis) served in how many of these PCs (x axis).

parity. We can see, for example, that one member served in 8 PCs, and four members served in 7.

The list we compiled was helpful in drafting the committee. When sending heavy member invitations, we allowed the candidates to accept as light or ERC, and when sending light member invitations, we allowed the candidates to accept as ERC. The number, type, and outcome of the invitations are specified in Table 4, and the demographic information of the resulting PC is specified in Table 5. Nearly 2/3 of the invitations sent were accepted, and as can be seen, this relatively high success rate is partially because we allowed candidates to opt for roles that involve a smaller reviewing load.

#### **Conflicts and Bidding**

#### 5.1 **Missing Conflicts**

Before assigning submissions to reviewers, it is important for the submission management system, HotCRP, to have accurate conflict of interest information as defined by the ATC '19 call for papers [19]. In addition to the conflict information that authors and reviewers explicitly specify, HotCRP helps by highlighting potential conflicts based on the information available to it, which is productive. This year, we also used the PC Chair Kit [3] that was written for ISCA '18 to find

| invite | invite | accepted | accepted | accepted | declined |

|--------|--------|----------|----------|----------|----------|

| type   | sent   | as heavy | as light | as ERC   |          |

| heavy  | 131    | 66       | 16       | 3        | 46       |

| light  | 22     | -        | 12       | 3        | 7        |

| ERC    | 27     | -        | -        | 16       | 11       |

| sum    | 180    | 66       | 28       | 22       | 64       |

Table 4: Number of invitations to serve on the ATC '19 committee sent to candidates, and the corresponding responses.

| seniority | junior      | 31 | country | country USA |   |

|-----------|-------------|----|---------|-------------|---|

|           | senior      | 63 |         | Canada      | 7 |

| gender    | female      | 14 |         | Switzerland | 6 |

|           | male        | 80 |         | Israel      | 4 |

| sector    | university  | 64 |         | UK          | 4 |

|           | industry    | 25 |         | Germany     | 2 |

|           | both        | 5  |         | Netherlands | 2 |

| continent | N. America  | 69 |         | Korea       | 2 |

|           | Europe      | 15 |         | Australia   | 1 |

|           | Asia        | 5  |         | China       | 1 |

|           | Middle East | 4  |         | France      | 1 |

|           | Australia   | 1  |         | Hong Kong   | 1 |

|           |             |    |         | Sweden      | 1 |

| -         |             |    |         |             |   |

Table 5: Demographic information of the PC (heavy and light, excluding program co-chairs).

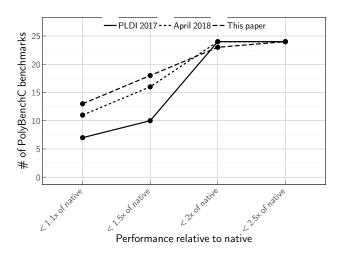

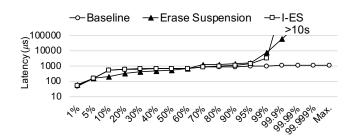

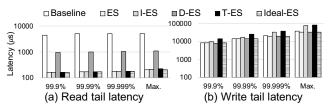

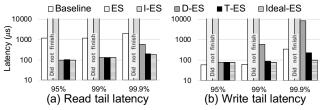

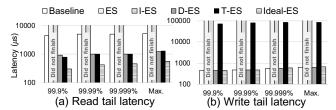

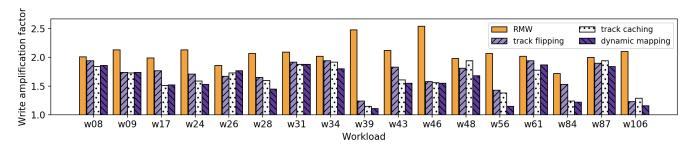

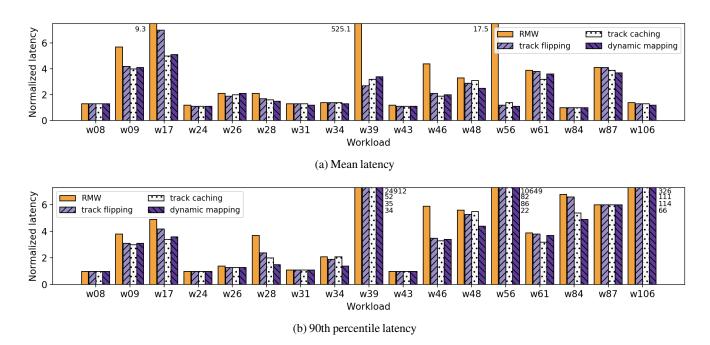

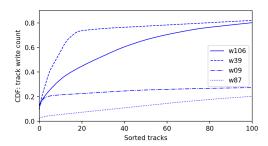

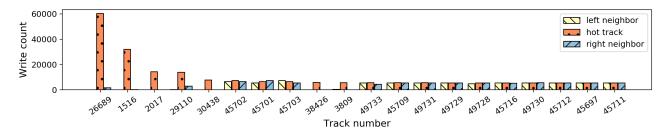

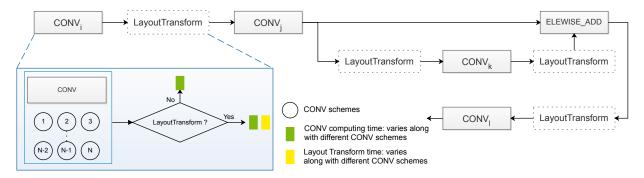

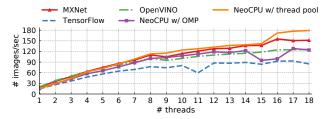

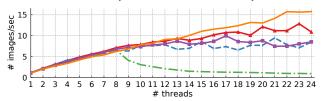

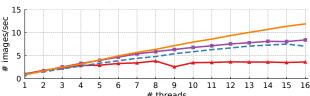

missing conflicts based on authorship information available via DBLP.<sup>2</sup> The script downloads the relevant DBLP information and checks if there are any co-authors of submission authors from the last n years that are not already listed as HotCRP conflicts.